با توجه به تغییرات سریع و مهم اقتصادی و زیست محیطی در سطح جهان، شتاب فزاینده پیشرفت های فناوری موجب شده مقامات و مسئولان شهری برای فائق آمدن بر مشکلاتی مانند تغییرات آب و هوایی، شلوغی و ترافیک شهرها و جمعیت پا به سن گذاشته خود به دنبال راهکارهای جدیدی باشند. هرچه شهرها بهتر و بیشتر از فناوری های پیشرفته برای مقابله با این مشکلات استفاده کنند، می توان آنها را هوشمندتر تلقی کرد. در ادامه به چند شهری اشاره می شود که براساس گزارش های مختلف در زمینه مدیریت شهری، می توان آنها را در زمره موفق ترین شهرها در هوشمندسازی معرفی کرد.

1. سنگاپور

«سنگاپور» (پایتخت کشور جمهوری سنگاپور) که یکی از مراکز مهم تجاری و مالی در جهان به شمار می آید، در حال حاضر می تواند نام هوشمندترین شهر در جهان را نیز به خود اختصاص دهد. این شهر عمده فعالیت های خود را با اتکا به فناوری های پیشرفته انجام می دهد. سنگاپور این هدف را دارد که به اولین کشور هوشمند در جهان تبدیل شود.

تقریبا هر فعالیتی در این شهر، توسط حسگرهایی نظارت می شود که شرکت های خصوصی آنها را ارائه کرده و هدف آن ها جمع آوری مجموعه فراوانی از اطلاعات است. این اطلاعات از سوی برنامه ای به نام «سنگاپور مجازی» بررسی می شود؛ مقامات سنگاپور با کمک این برنامه بهترین راهکارها را برای مدیریت شهر پیدا می کنند.

پیام هشداری به بستگان آنها فرستاده می شود. «درمان از راه دور» نیز یکی دیگر از سیستم هایی است که به بیماران اجازه می دهد بدون خروج از خانه، از طریق صفحه های ویدئویی با پزشک خود ارتباط برقرار کنند.

با این حال یکی از مسائل مهم این است که بخش زیادی از این اطلاعات شخصی است و یکی از نگرانی های مهم درباره شهرهای هوشمند، مقوله حریم شخصی شهروندان است؛ در همین زمینه، سنگاپور در سال های اخیر متعهد به شفافیت بیشتر و شناسایی نگرانی ها در این زمینه شده است.

2. بارسلون

در سال های اخیر «بارسلون» مشکلات فراوانی در زمینه جمعیت پا به سن گذاشته و رکود محلی خود داشته است؛ بر همین اساس مسئولان این شهر سعی کرده اند با کمک فناوری های پیشرفته، زیرساخت های آن را ارتقا بخشند و مشاغل جدید ایجاد کنند. علاوه بر محل های پارک هوشمند و سیستم های ترافیکی، این شهر در زمینه انرژی نیز روش های منحصر به فردی دارد.

بارسلون در مقایسه با تمام شهرهای پیشرفته، میزان بیشتری از نور خورشید را دریافت می کند و توانسته با راهکارهایی بهترین استفاده را از این مزیت ببرد.

در سال 2000 تمام ساختمان های این شهر برای تولید آب گرم مورد نیاز خود ملزم به استفاده از سیستم های خورشیدی شدند. وجود ناوگان اتوبوس های هیبریدی موجب شده بارسلون یکی از سالم ترین سیستم های حمل و نقل عمومی را داشته باشد. همچنین 400 ایستگاه دوچرخه سواری در این شهر وجود دارد که استفاده کنندگان از این دوچرخه ها یا به صورت سالانه اشتراک می گیرند یا از طریق گوشی های همراه خود هزینه آن را پرداخت می کنند.

سیستم دفع زباله آن نیز در نوع خود منحصر به فرد است، به گونه ای که وجود لوله هایی در زیر سطل های زباله برای انتقال آنها به مخازن اصلی، نیاز به ماشین های حمل زباله را از بین برده است. تعدادی از اپلیکیشن های هوشمند نیز به کمک فعالیت های روزانه شهروندان آمده اند؛ یکی از آنها اپلیکیشنی است که به عنوان صدای شهروندان عمل می کند و آنها می توانند شکایت های خود از خدمات شهری را مانند خرابی خیابان ها یا شکسته شدن چراغ های راهنمایی به اطلاع مسئولان برسانند.

3. اسلو

مانند بسیاری از شهرهای منطقه اسکاندیناوی، «اسلو» می کوشد با استفاده از این فناوری ها هرچه بیشتر در مسیر پیشرفت و سلامت قرار بگیرد. از سوی دیگر تعهد مسئولان این شهر به استفاده از برنامه های هوشمند در زمینه انرژی موجب شده پایتخت نروژ یکی از بادوام ترین شهرهای هوشمند در جهان باشد.

یکی دیگر از راهکارهای منحصر به فرد مسئولان اسلو مربوط به تولید انرژی است که به جای دفن زباله های صنعتی و استاندارد از آنها برای تولید انرژی استفاده می کنند. نکته جالب اینجاست که مسئولان اسلو به قدری از زباله ها در راستای این هدف استفاده کرده اند که در سال 2013 ذخیره زباله آنها به پایان رسید و مقامات دستور واردات زباله از خارج از کشور را صادر کردند.

4. لندن

هم زمان با بزرگ تر شدن «لندن» و بیشتر شدن سن جمعیت آن، زیرساخت های این شهر نیازمند توجه و دقت بیشتری است. تخمین زده می شود ک جمعیت این کشور تا 10 سال آینده از یک میلیون نفر بیشتر شود. مسئولان این شهر برای مقابله با این مشکلات، روی فناوری پیشرفته حساب ویژه ای باز کرده اند. سیستم دوچرخه های الکترونیکی و بیش از 300 محل پارک هوشمند خودرو از جمله این اقدامات است که تاثیرهای مثبت فراوانی نیز به همراه داشته است.

همچنین پروژه ای در این شهر آغاز شده که می کوشد با سرمایه گذاری، رودخانه تیمز را به یکی از منابع اصلی انرژی تبدیل کند. برای دسترسی به انرژی سبز نیز مسئولان لندن قصد دارند استفاده از صفحه های خورشیدی در بالای ساختمان های مسکونی را افزایش دهند.

محققان پژوهشکده فرآوری مواد معدنی جهاد دانشگاهی تربیت مدرس موفق به تولید کاغذ معدنی برای اولین بار در کشور در مقیاس پایلوت شدند.

مهدی ذاکری، سرپرست پژوهشکده فرآوری مواد معدنی جهاد دانشگاهی تربیت مدرس از موفقیت محققان این پژوهشکده در تولید کاغذ معدنی از کربنات کلسیم میکرونیزه خبر داد و گفت: کاغذ سنگی، نسل جدیدی از کاغذ است که اخیرا برای کاربریهای مختلف مورد توجه پژوهشگران قرار گرفته است.

وی افزود: مواد اولیه این کاغذ، کربنات کلسیم و مواد پلیمری بوده که میتواند جایگزین استفاده از چوب برای تولید کاغذ شود.

ذاکری با بیان اینکه محققان پژوهشکده فرآوری مواد معدنی جهاد دانشگاهی با انجام تحقیقات گسترده موفق به تولید نمونه این کاغذ در مقیاس پایلوت شدند، خاطرنشان کرد: ضد آب بودن، مقاوم در برابر پارگی و برگشتپذیری آن به خاک طی دوره بازیافت کوتاه مدت از جمله خواص این نوع کاغذ است.

سرپرست پژوهشکده فرآوری مواد معدنی جهاد دانشگاهی تربیت مدرس با اشاره به مصرف بالای سرانه کاغذ در کشور و امکان جایگزینی این محصول با کاغذهای معمولی، از این دستاورد به عنوان مصداق بارز تحقق شعار سال مبنی بر «اقتصاد مقاومتی؛ تولید و اشتغال» یاد کرد.

عضو هیات علمی جهاد دانشگاهی همچنین کاربردهای این محصول را در بستهبندی و چاپ عنوان کرد.

ذاکری، کاغذ تولیدشده توسط محققان پژوهشکده فرآوری مواد معدنی جهاد دانشگاهیتربیت مدرس را دوستدار محیط زیست عنوان و تصریح کرد: در فرآیند تولید کاغذ سنگی نه تنها از آب استفاده نمیشود، بلکه نیازی به استفاده از سفیدکنندهها هم وجود ندارد که این امر به سازگاری این محصول با محیط زیست نیز کمک خواهد کرد.

رییس دپارتمان نجوم دانشگاه آریزونا اعلام کرد بین 10 تا 15 سال آینده بشر اولین نمونههای حیات بیگانه را در فضا کشف خواهد کرد.

به نقل از دیلیمیل، پروفسور "کریس ایمپی" (Chris Impey) معتقد است با توجه به پیشرفت تجهیزات تحقیقاتی و رصدی در فضا نظیر تلسکوپ فضایی "جیمز وب"(James Webb)، فاصله محققان تا کشف اولین نمونههای حیات بیگانه در فضا کمتر از 20 سال است اما این حیات هوشمند نبوده بلکه محدود به نمونههای میکروبی و باکتریایی خواهد بود.

ایمپی افزود: بیشترین شانس ما برای کشف حیات در فضا در محدوده منظومه شمسی است و باید ابتدا تمرکز خود را به فضای نزدیک موجود اختصاص دهیم.

وی خاطرنشان کرد: برای مثال در مریخ اگر حیات میکروبی وجود داشته باشد احتمالا در سطوح زیرین آن باید به دنبال آن گشت اما هنوز هم ممکن است نشانههایی از حیات در گذشته آن از دید ما پنهان مانده باشد.

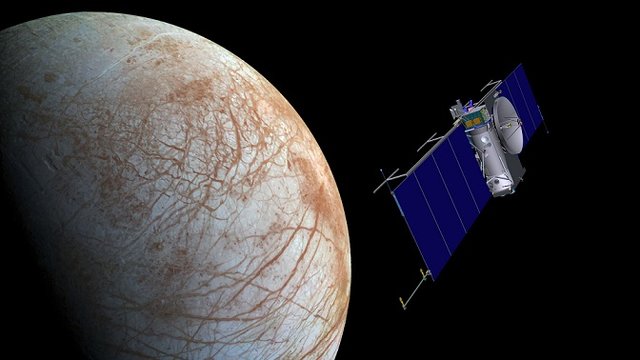

ایمپی در مصاحبه خود به ششمین قمر بزرگ مشتری موسوم به "اروپا"نیز اشاره کرده است.

این قمر خواصی مشابه زمین از جمله هسته متشکل از آهن و همچنین اقیانوسهای آب شور دارد که کل سطح آن را پوشانده و به خاطر فاصله آن از خورشید و دمای پایین، منجمد شده است.

"سازمان فضایی آمریکا"(ناسا) و "آژانس فضایی اروپا"(ایسا) قصد دارند برای شناخت بیشتر این قمر مطالعات پیشرفتهای بر روی آن انجام دهند.

در سال گذشته محققان نشانههایی از وجود حیات بیگانه در یکی از قمرهای منجمد زحل موسوم به "انسلادوس"( Enceladus) پیدا کردند که نشان میداد تمام موارد مورد نیاز برای پشتیبانی از حیات بیگانه را دارد.

مهمترین پدیدهای که محققان در فضا به دنبال آن هستند، وجود حیات بیگانه است و باید دید که پیشبینی این استاد دانشگاه آریزونا محقق میشود یا خیر.

آمار فروش اخیر پورشه بسیار جالب توجه است و مدل قدرتمند و گرانقیمت 911 توربو S توانسته است در بازار ایالات متحده، فروشی بیشتر از مدل 9111 غیر توربو داشته باشد. به نظر میرسد خریداران تمایلی به صرفهجویی ندارند و بهسادگی به سمت مدلهای گرانقیمت میروند و گرانترین مدل 911 را خریداری میکنند. متأسفانه پورشه برای خریدارانی که میخواهند پول بیشتری خرج کنند تا ظاهر خودروی آنها جذابتر شود؛ چیزی بیش از انتخاب تودوزی سفارشی یا رنگهای بدنهی خاص ارائه نمیدهد و بنابراین خودروی آنها نمیتواند خیلی با سایر پورشهها تفاوت داشته باشد. گویا پورشه سرانجام تصمیم گرفته است به درخواست مشتریان خود پاسخ دهد و مدلی ویژه از 911 توربو S را روانهی بازار کند. این خودروی تولید محدود با نام کامل 911 Turbo S Exclusive Series وارد بازار خواهد شد که در ادامه، به ویژگیهای آن خواهیم پرداخت.

این مدل جدید با یک کیت بدنهی آیرودینامیک جدید به بازار خواهد آمد که شامل نمای عقب متفاوت، کالیپرهای ترمز مشکی، سیستم اگزوز جدید و گلگیرهای جدیدی با نام Manufaktur هستند. برای هرچه خاصتر شدن ظاهر این خودرو، یک رنگ ویژهی زرد طلایی نیز برای نسخهی اکسکلوسیو 911 توربو S قابل انتخاب است که زیبایی چشمنوازی در ترکیب با تودوزی مشکی و رینگهای سیاه این خودرو ایجاد میکند. البته مشتریان میتوانند سایر رنگها را نیز برای خودروی خود انتخاب کنند.

در داخل کابین این مدل شاهد طراحی متفاوتی هستیم؛ بهطوری که نوارهای طلایی در سرتاسر کابین وجود دارند و تا پشتسریهای صندلیها امتداد یافتهاند. در جایجای کابین نیز استفاده از الیاف کربن به چشم میخورد که در کنار خط دوخت مسیرنگ کابین، ترکیب زیبایی پدید آورده است.

گرچه تغییراتی که در بالا ذکر کردیم نکات جذاب و جالب توجهی در بر داشتند؛ اما جذابترین بخش این خودرو همانند هر پورشهای، پیشرانهی آن است. پیشرانهی ۳.۸ لیتری شش سیلندر این خودرو که از نوع تخت یا باکسر است، یک کیت افزایش قدرت دریافت کرده تا توان آن از ۵۸۰ اسب بخار به ۶۰۷ اسب بخار برسد. گشتاور تولیدی این پیشرانه به عدد ۷۵۰ نیوتونمتر رسیده است که با استفاده از جعبهدندهی محبوب و کارآمد ۷ سرعتهی دوکلاچه موسوم به PDK، به هر چهار چرخ خودرو منتقل میشود. زمان رسیدن این خودرو از سرعت صفر به ۱۰۰ کیلومتر بر ساعت، تنها ۲.۸ ثانیه است و حداکثر سرعت آن به ۳۲۹ کیلومتر بر ساعت میرسد. برای ثبت سرعت ۲۰۰ کیلومتر از حالت سکون، این خودرو تنها ۹.۶ ثانیه احتیاج دارد که در مقایسه با مدل توربو S استاندارد، ۳ دهم ثانیه بهتر است.

خریداران این خودرو میتوانند یک ساعت کرونومتردار پورشه دیزاین نیز خریداری کنند که دارای رنگی مشابه با رنگ خودرو خواهد بود. پورشه این ساعت ویژه را بهطور خاص برای خریداران این مدل طراحی و عرضه کرده است.

قیمت پورشه 911 توربو S اکسکلوسیو، از ۲۵۸ هزار و ۵۵۰ دلار آغاز میشود که حدود ۶۰ درصد، در مقایسه با مدل استاندارد توربو S گرانتر است؛ اما تولید این خودرو تنها به ۵۰۰ دستگاه محدود خواهد شد که در آینده آن را تبدیل به محصولی خاص خواهد کرد.

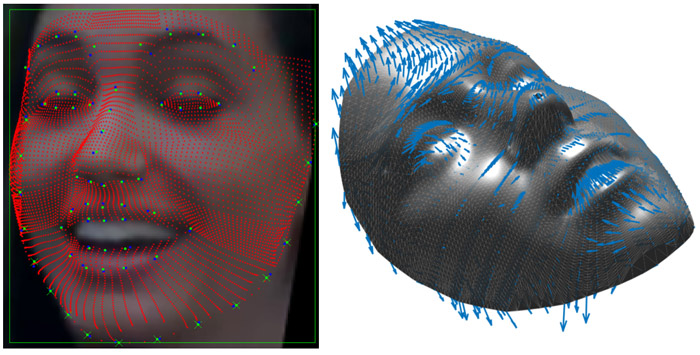

یکی از چالشهای کنونی جراحان پلاستیک این است که مرجع مشخصی برای بازسازی چهرهی قومیتها و سنهای مختلف در دست ندارند. این یعنی در جراحیهای ترمیمی کنونی، کارایی اعضای صورت بازمیگردد؛ ولی ظاهر آن با ظاهر طبیعی فردی با همان سن و سال و قومیت همخوانی ندارد. هماکنون یک گروه تحقیقاتی از امپریال کالج لندن و بیمارستان عمومی سلطنتی انگلستان از بازدیدکنندگان موزهی علوم درخواست میکنند تا برای اسکن چهره داوطلب شوند. این تحقیقات با هدف ساختن یک پایگاه اطلاعاتی از مدلهای سه بعدی چهره با حالتهای مختلف، قومیتها و نژادهای مختلف و بازهی سنی وسیع صورت میگیرد. در نهایت این پایگاه اطلاعاتی به جراحان پلاستیک به ترمیم صورت با کارایی صحیح و همچنین ظاهری کاملا طبیعی کمک خواهد کرد. همچنین این گروه تحقیقاتی کاربردهای دیگری نیز برای این فناوری پیشبینی میکنند. درک بهتر فرایند تکامل انسان، سازوکار دستگاههای دروغسنجی و حتی کمک به کودکان مبتلا به اوتیسم، از جملهی این کاربردها هستند.

این پروژه ابتدا در سال ۲۰۱۲ با مشارکت بیمارستان بزرگ اورموند و تحت سرپرستی دکتر دیوید دوناوی کلید خورد. در این پروژه ۱۲,۰۰۰۰ داوطلب از بین بازدیدکنندگان موزهی علوم با سنین و قومیتهای مختلف مورد اسکن چهره (بدون داشتن حالت خاصی مانند اخم یا لبخند) قرار گرفتند.

گروهی که در سال ۲۰۱۷ در حال بررسی و اسکن چهرهی داوطلبان هستند، حالتهایی مانند خشم و ناراحتی و... را نیز به این آزمون اضافه کردهاند تا مدل سهبعدی کامپیوتری نهایتا بتواند چنین حالتهایی را نیز بازسازی کند. دکتر آلن پونیا سرپرست دوم این گروه تحقیقاتی از بیمارستان عموم سلطنتی انگلستان میگوید:

هدف ما توسعهی مدلهای سه بعدی رایانهای است تا بهعنوان مرجعی برای عملهای ترمیمی چهره استفاده شوند. البته هنوز چند سالی با استفادهی عملی این سازوکار در جراحیها فاصله داریم ولی نتایج کنونی بسیار امیدبخش هستند. کاربردهای این پروژه میتوانند زندگی ما را عوض کنند. برای مثال اگر ما بخواهیم صورت یک دختربچهی ۵ سالهی چینی را بازسازی کنیم، کامپیوتر ما تمامی ابعاد و مشخصات طبیعی مربوط به چنین سن، جنس و قومیتی را در اختیار جراحان میگذارد.

این دادهها از گروه تحقیقاتی موزهی علوم انگلستان و همچنین گروهی به سرپرستی دکتر استفانوس زایفریو در امپریال کالج گرد هم میآیند. برای یک دههی گذشته، این گروهها سازوکاری ساختهاند که هزاران چهره را در چند ساعت بررسی میکند. اگر این سازوکار بخواهد توسط انسان اجرا شود، سالها زمان خواهد برد. این برنامه تمام ویژگیهای چهره از ویژگیهای بارزی مانند مکان و ابعاد حدقهی چشمها، بینی و پیشانی تا مشخصات جزئیتری مانند پوست و حالت گوشهی لبها را ثبت و بررسی میکند. با کمکگیری از مقایسهی مستقیم چنین دادههایی، گروه موفق شده است مدلی آماری از یک چهرهی کاملا متوسط در سنین مختلف و قومیتهای مختلف به دست آورد.

از داوطلبان موزهی علوم در آزمون جدید خواسته میشود حالتهای مختلفی شامل بیزاری، خشم، ترس، غم، تعجب و درد را نیز به خود بگیرند. همچنین از آنها خواسته میشود لبهایشان را غنچه کنند، پرههای بینی خود را باز کنند یا لپهایشان را باد کنند! این حرکات از نظر پزشکی با حالات بیماران مبتلا به فلج صورت (facial palsy) بر اثر سکتههای مختلف مرتبط است.

دکتر زایفریو از گروه کامپیوتر امپریال کالج در این باره میگوید:

کار کردن با دکتر پونیا در این پروژه یک موقعیت بزرگ بوده است. اکنون ما میتوانیم انقلابی در جراحیهای ترمیمی چهره به وجود آوریم. ما نهتنها صدها مشخصهی ظاهری چهره را بررسی و ثبت میکنیم؛ بلکه مشخصات اجزای زیر پوست مانند استخوانها و ماهیچهها را نیز برای طراحی هرچه واقعیتر چهره در نظر میگیریم. ما در نظر داریم در آینده بیش از این پیش برویم و از روی ویدئوهای قدیمی، غالب سهبعدی صورت افراد را بازسازی کنیم. به این طریق میتوانیم دقیقترین مدلها را برای عمل جراحی پلاستیک جوانسازی افراد از خودشان داشته باشیم. این طبیعیترین چهرهی ممکن از آنها را در پی خواهد داشت.

کاربردهای جدید این فناوری

کاربردهای این فناوری بسیار بیش از حیطهی پزشکی را در بر خواهند گرفت؛ برای مثال برای توسعهی سیستمهای تشخیص هویت. دکتر زایفریو در توضیح میگوید:

برای مثال خود من با تصویرم در گواهینامهام زمین تا آسمان فرق دارم. این برای کارتهای شناسایی برای موقعیتهایی مانند فرودگاه هم صدق میکند. بر اساس این تکنولوژی، یک دوربین میتواند گذرنامه یا کارت هویت من را به همراه چهرهام اسکن کند و با استفاده از فناوری مدلسازی سهبعدی چهرهی جوانتر یا مسنتر من را تشخیص دهد. کمک به کودکان مبتلا به اوتیسم نیز یک کاربرد دیگر است. برخی از این کودکان در تشخیص حالت چهرهی افراد و مرتبط کردن آن با احساسات آنها مانند شادی یا ناراحتی مشکل دارند. برخی نیز نمیتوانند احساسات خود را بروز دهند. بر اساس این فناوری، پدر و مادر این کودکان میتوانند یک برنامهی کاربردی روی گوشی خود نصب کنند و با اسکن چهرهی کودکشان با دوربین موبایل و سپس آنالیز آن توسط برنامهی ما، متوجه حالت احساسی کودکشان بشوند. این کار بهصورت عکس برای کودکان اوتیسمی برای درک حالات چهرهی دیگران نیز ممکن است.

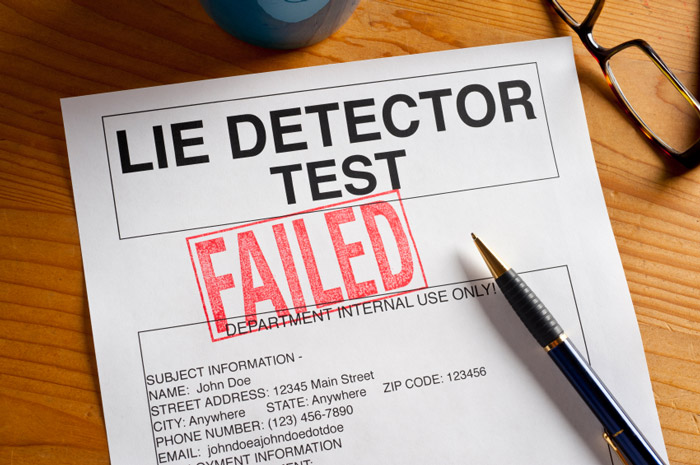

کاربرد دیگر در دروغسنجی است. در این کاربرد یک دوربین، تمام حالات چهرهی یک فرد را در مقیاس میکرو اسکن میکند و مشخص میکند که فرد چه زمانی در حال دروغ گفتن است.

همچنین گروه تحقیقاتی بر این باورند که میتوانند با استفاده از فناوری اخیر، از برخی رازهای تکامل انسان نیز پرده بردارند. در حال حاضر فرآیند بازسازی چهرهی انسانهای اولیه از روی قطعات استخوانهای جمجمهی باقیمانده، کاری بسیار زمانبر و طاقتفرسا است. با اسکن این استخوانها و سپردن آنها به این فناوری، میتوان ظرف چند دقیقه یک چهرهی ماقبل تاریخ را بازسازی کرد. با این روش میتوان خط سیر زمانی و تأثیر آن بر تکامل چهرهی انسانها را بسیار راحتتر و دقیقتر بررسی کرد.

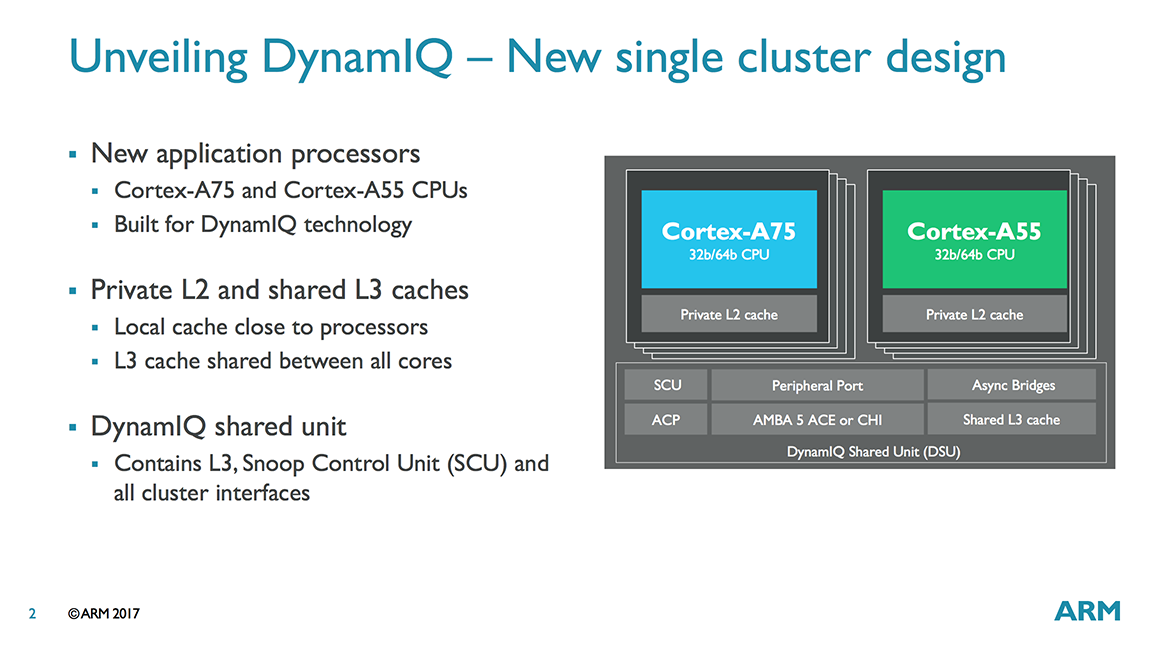

تغییرات هستههای جدید کورتکس ARM را میتوان به دو بخش «استفاده از معماری جدید و بهبودهای کلی» و«ریزمعماری جدید هستههای A75 و A55» تقسیم کرد. در قسمت قبل با بخش اول و بهویژه تکنولوژی DynamIQQ آشنا شدیم و دیدیم که فناوری جدید آرم چگونه با فراهم کردن امکان بهکارگیری هستههای قوی و پرمصرف (big) در کنار هستههای ضعیف و کممصرف (LITTLE) درون یک کلاستر، قرار است جایگزین تکنیک big.LITTLE در سیستمهای روی چیپ (SoC) مبتنی بر معماری آرم شود.

در این قسمت و قسمت آینده، به بررسی تغییرات ریزمعماری هسته میپردازیم.

ریزمعماری Cortex-A75

کورتکس A75 جدیدترین عضو از خانوادهی CPU-های آرم با نام «سوفیا» است که شامل هستههای A12، A17 و A73 میشود. درست مانند هستههای A72 و A57 که هر دو متعلق به خانوادهی آستین بودند و شباهتهای زیادی با یکدیگر داشتند، ریزمعماری A75 نیز بسیار شبیه به A73 است.

آرم در طراحی A73 تمرکز خود را بر بهینگی مصرف انرژی و پایینآوردن دمای پردازنده گذاشته بود؛ درحالیکه در A75، تمرکز اصلی بر افزایش عملکرد هسته و اضافه کردن قابلیتهای جدید بوده است. آرم برای دستیافتن به این هدف تغییرات عمدهای در پایپلاین هسته داده است. استفاده از تکنولوژی DynamIQ نیز برای رسیدن به این هدف چندان بیتأثیر نبوده است. قابلیتهای جدید هسته اما همگی به لطف مهاجرت از معماری ARMv8.0 به ARMv8.22 به وجود آمدهاند.

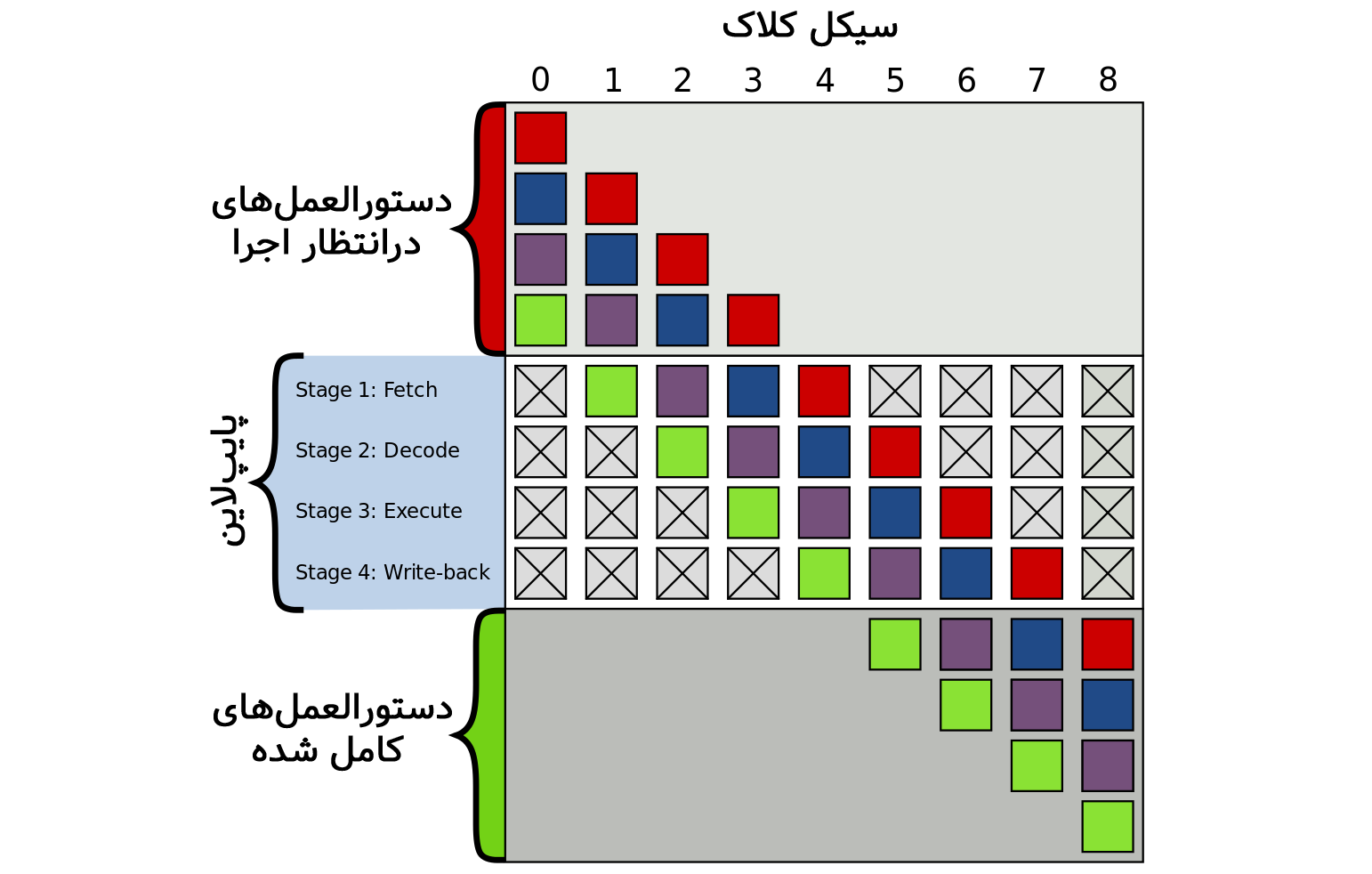

پیش از ادامه، بد نیست با مفهوم پایپلاین بهصورت مختصر آشنا شویم.

نمونهای از یک پایپلاین ۴ مرحلهای. مربعهای رنگی نشاندهندهی دستورالعملهای مستقل از یکدیگر هستند

«پایپلاین کردن دستورالعمل» (Instruction Pipelining) به تکنیکی گفته میشود که در آن پردازنده مراحل مختلف یک دستورالعمل یا چندین دستورالعمل را بهصورت موازی پردازش میکند. با استفاده از تکنیک پایپلاین، بهجای پردازش هر دستورالعمل در یک سیکل کلاک پردازنده، دستورالعملها در چندمرحله بهصورت همزمان و خارج از نوبت پردازش میشوند. تعداد استیجها یا مراحل پایپلاین به معماری پردازنده بستگی دارد. برای مثال، مراحل پایپلاین کلاسیکRISC از این قرار است:

۱- گرفتن دستورالعمل از حافظه (Fetch)

۲- دیکود کردن دستورالعمل (Decode)

۳- اجرای دستورالعمل (Execute)

۴- دسترسی به مموری (Memory)

۵- بازنویسی نتیجه (Write Back)

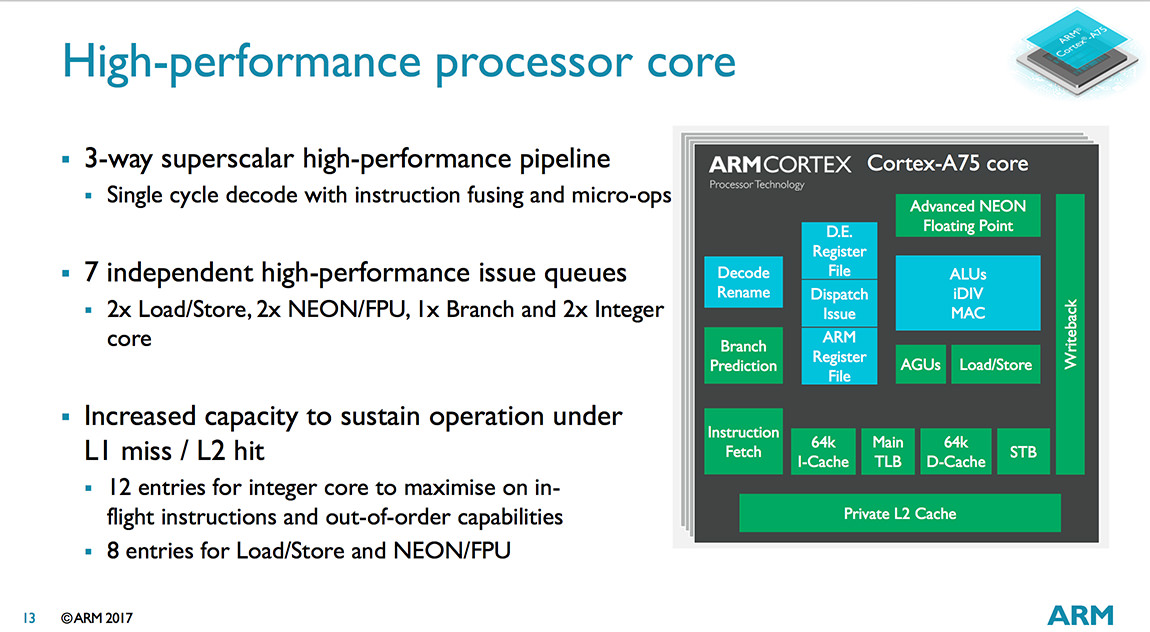

A75 از یک پایپلاین نسبتا کوتاه ۱۱ تا ۱۳ مرحلهای مشابه با A73 استفاده میکند. گرفتن دستورالعمل در هستهی جدید هنوز هم ۴ مرحلهای است و دیکودر همچنان قادر است اکثر دستورالعملها را در یک سیکل دیکود کند؛ هرچند دیکود کردن میکرو عملیات (µops) که از مجموعه دستورالعملهای NEON/FP استفاده میکنند، به یک مرحلهی دیگر نیز احتیاج دارد. بزرگترین تفاوت A75 با A73 از لحاظ مراحل پایپلاین، استفاده از دیکود ۳ مرحلهای است که در ادامه دربارهی آن بیشتر توضیح خواهیم داد.

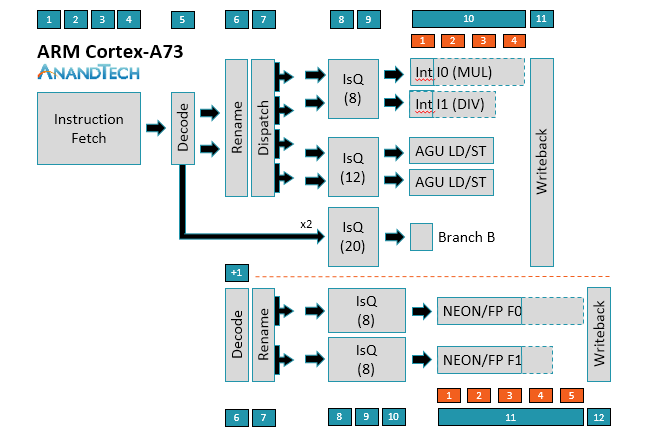

دیاگرام استیجهای پایپلاین هستهی Cortex-A73. قسمت بالا مربوط به محاسبات صحیح و قسمت زیر خطچین، مربوط به محاسبات ممیز شناور است

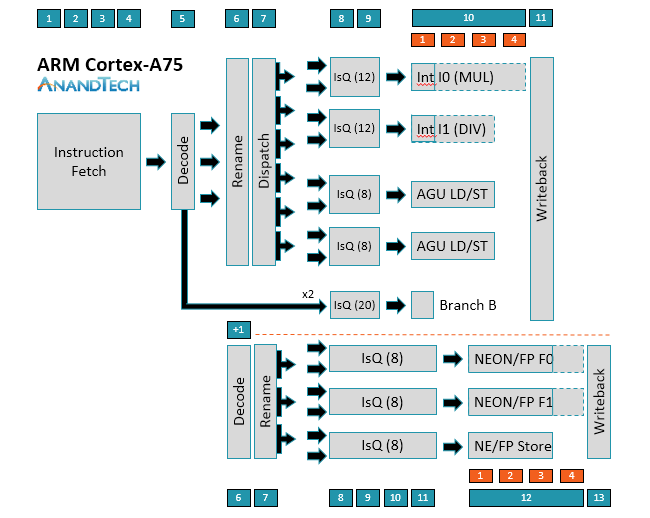

دیاگرام استیجهای پایپلاین هستهی Cortex-A75. قسمت بالا مربوط به محاسبات صحیح و قسمت زیر خطچین، مربوط به محاسبات ممیز شناور است

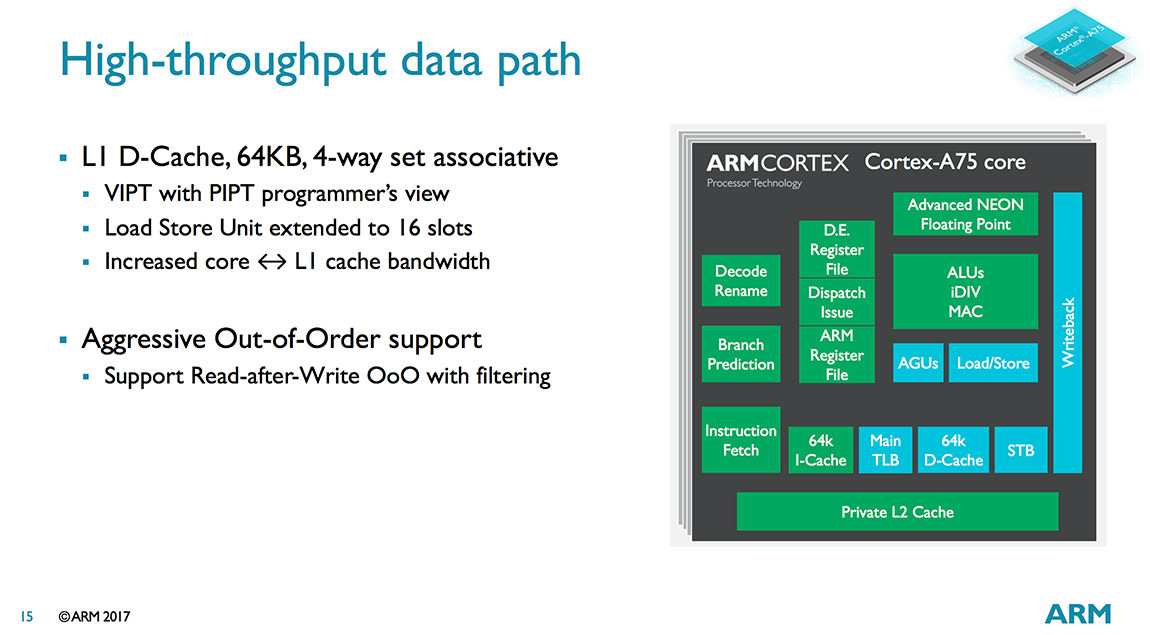

قابلیت دیکود کردن ۳ دستورالعمل در هر سیکل بهمعنای آن است که A75 میتواند تا ۶ میکرو عملیات را در هر سیکل (µops/cycle) بهانجام برساند. از محاسبات ممیز شناور که بگذریم، به محاسبات صحیح میرسیم. همانطور که از نمودارهای بالا مشخص است، در A75 برخلاف A73 هر ۲ واحد محاسبه و منطق (ALU) و واحد تولید آدرس (AGU)بهجای استفاده از یک صف عملیات بهصورت اشتراکی، صف اختصاصی خود را دارند و A75 میتواند تا ۲ میکرو عملیات را در این صفها قرار بدهد. این موضوع باعث میشود اجرای خارج از نوبت دستورالعملها در A75 بهبود پیدا کند.

همانطور که در دیاگرام مشخص است، میکرو عملیات ساده میتوانند مراحل Rename و Dispatch را دور بزنند و در نتیجه عملا تأخیر ناشی از دو مرحله را حذف کنند. البته دستورالعملهای پیچیده که نیاز به دسترسی رجیسترها دارند، همچنان باید از دو مرحلهی Rename و Dispatch عبور کنند.

اگر دوباره به سمت محاسبات ممیز شناور و دستورالعملهای NEON/FP (قسمت پایینی دو نمودار) بازگردیم، متوجه خواهید شد که مرحلهی Dispatch در این قسمت وجود ندارد. همانطور که مشخص است، میکرو عملیاتها همچنان در صف قرار میگیرند، اما به دلیل حذف مرحلهی Dispatch، این صفها از صفوف قسمت پردازش صحیح دو مرحله زیادتر است.

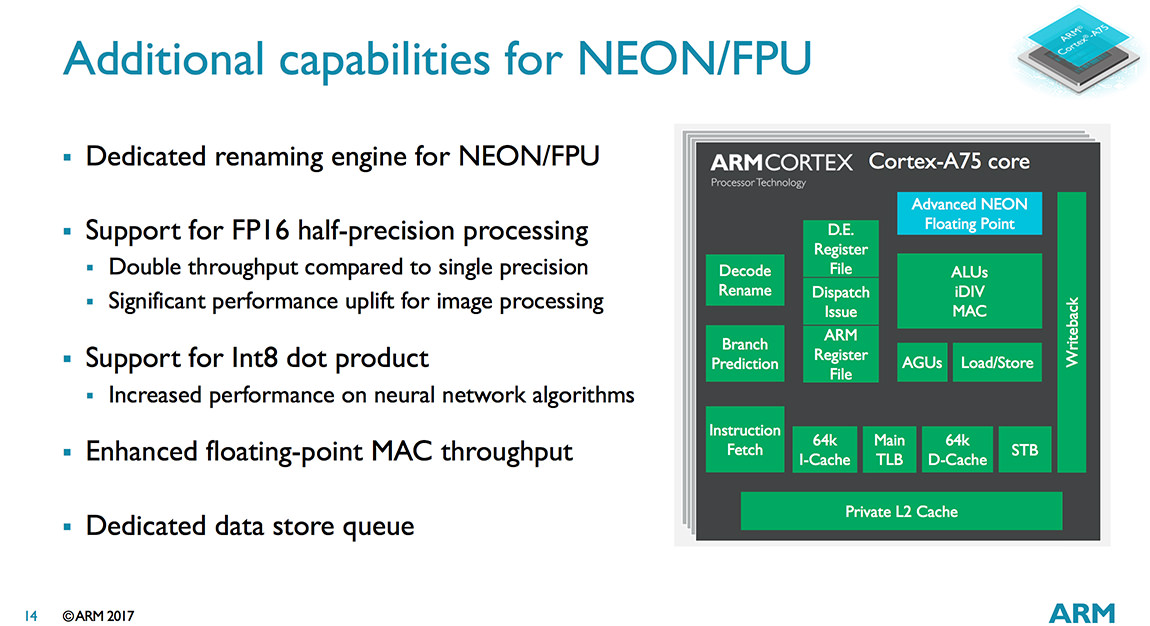

اگر قسمت محاسبات شناور A75 و A73 را با یکدیگر مقایسه کنیم، متوجه خواهیم شد تعداد صفها به سه عدد افزایش یافته است و دو میکرو عملیات در هر صف میتوانند قرار بگیرند که خود باعث شده است تعداد مراحل مرتبط با صف در A75 به ۴ مرحله افزایش پیدا کند. ARM میگوید هنگام طراحی ریزمعماری A75 افزایش تعداد ورودیهای هر صف را نیز بررسی کرده و در نهایت به این نتیجه رسیده است که افزایش توان مصرفی ناشی از این کار بیشتر از افزایش عملکرد پردازنده است. بههمین دلیل، آرم بهجای اضافه کردن تعداد ورودی به هر صف، تصمیم گرفته است یک پایپ جدید NEON/FP با صف اختصاصی خود ایجاد کند. با این کار میزان تأخیر عملیات ضرب تجمیعی (MAC) نیز از ۶ به ۵۵ سیکل کاهش پیدا کرده است.

A75 همچنان از «ریزمعماری اسلات محور» استفاده میکند که برای اولین بار همراه با A73 معرفی شد. آرم دربارهی این ریزمعماری بهجز اطلاعاتی که سال گذشته منتشر کرد، جزئیات بیشتری ارائه نداده است. تنها در همین حد میدانیم که در این ریزمعماری ۸ «اسلات» وجود دارد که وظیفهی آنها از بین بردن دسترسی بیمورد و غیر ضروری به منابع سیستمی در بلوک دستورالعمل است که در نهایت منجر به کاهش مصرف انرژی میشود.

هم A73 و هم A75 از یک واکشِ اولیهی دستورالعمل استفاده میکنند (Instruction Prefetch یا واکشی اولیهی دستورالعملها، نام تکنیکی است که در آن برای بالارفتن سرعت و پایین آمدن تأخیر، دستورالعملها یا اطلاعات قبل از اینکه حتی به آنها نیاز باشد از رم کشیده و درون کش قرار داده میشوند). این واکشِ اولیه وظیفهی تغذیهی یک کش ۶۴ کیلوبایتی L1 را برعهده دارد.

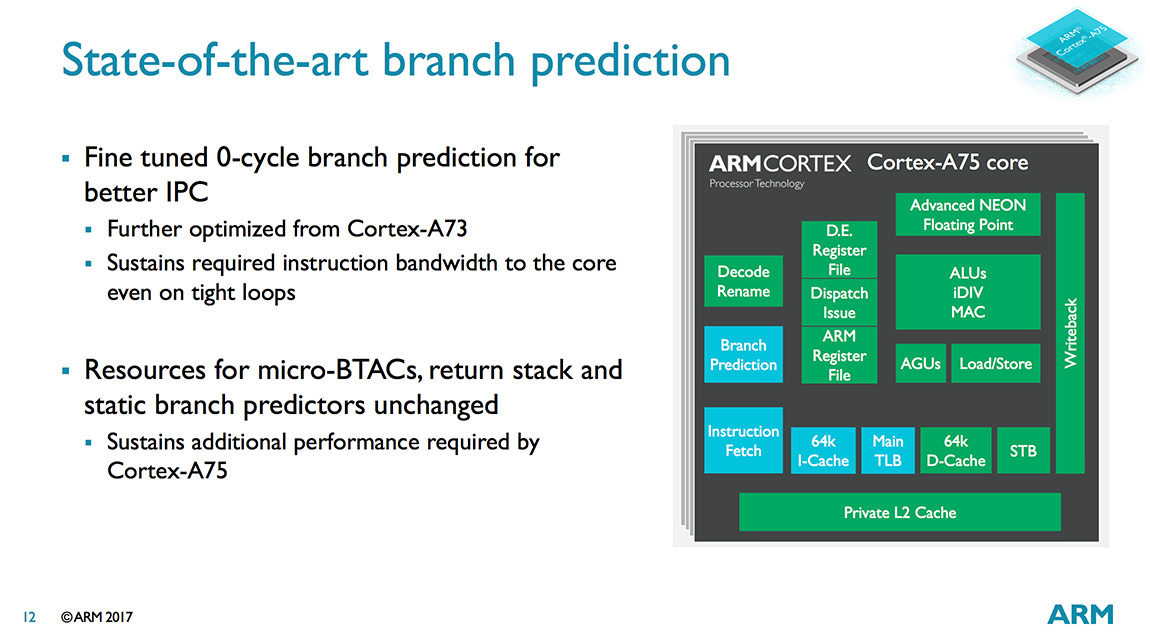

پیشبینی کنندهی پرش (Branch Predictor) هستهی A75 شاهد بهبود جزئی نسبت به A73 بوده است

آرم در A73 برای اولین بار از یک پیشبینیکنندهی پرش (Branch Predictor، مداری که سعی میکند مسیر یک پرش را قبل از اینکه قطعی شود حدس بزند) جدید برای بالابردن سرعت پیشبینی استفاده کرد. هنگام طراحی A75، آرم متوجه شد که پیشبینیکنندهی پرش A73 همچنان عملکرد رضایتبخشی دارد و افزایش دادن بیش از پیشِ عملکرد آن، ارزش بالا رفتن توان مصرفی پردازنده را ندارد. به همین دلیل در ریزمعماری A75 دقیقا از همان پیشبینیکنندهی پرش A73 استفاده شده است.

همانطور که بالاتر اشاره کردیم، آرم که در A73 از فرآیند دیکود دو مرحلهای استفاده میکرد، تعداد مراحل دیکود را در A75 به سه مرحله افزایش داده است. آرم همواره به دنبال یافتن راهی برای افزایش IPC (دستورالعمل در سیکل) در پردازندههای خود است. درحالیکه پردازندههایی با تراشهی بزرگتر نیز در بنچمارک SPECint 2006 بهزحمت به IPC بالای ۲ میرسند؛ آرم با A73 توانسته بود در این بنچمارک به امتیاز ۱.۲ و در شرایط خاص به ۱.۶ تا ۱.۸ برسد.

البته این به معنای آن نیست که دیکودر ۲ مرحلهای استفاده شده در این هسته کافی بوده است؛ چرا که در شرایط خاصی که به خروجی بیشتر از پردازنده نیاز است، IPC پردازندههای مجهز به A73 به ۰.۶ تا ۰.۴ نیز افت میکرد. بهعنوان مثالی ازشرایط خاص، میتوان به مواقعی اشاره کرد که یک پرش در پیشبینی دچار اشتباه میشود (با احتمال ۲ تا ۴ بار در هر ۱۰۰۰ دستورالعمل) و نیاز است تا CPU صفها را با دستورالعملهای جدید پر کند. البته استفاده از یک صف و مرحلهی اضافه، مصرف هستههای جدید A75 را افزایش میدهد؛ اما این کار برای رسیدن به IPC مورد نظر آرم ضروری بوده است.

مراحل Rename و Dispatch در هستههای جدید درست مانند A73 و دیگر پردازندههای سری سوفیا باقی مانده است و همچنان خبری از بافر بازآرایی (ROB) نیست. در عوض A75 از یک فایل فیزیکی رجیستر برای ذخیرهی میکرو عملیات استفاده میکند که با کاهش انتقال اطلاعات در سطح پردازنده و از بین بردن یک سری باتلنک، باعث میشود مصرف هسته کاهش پیدا کند.

از لحاظ مسیر انتقال اطلاعات، ریزمعماری جدید از یک واکشِ اولیهی بهبودیافته استفاده میکند. اگرچه واکش اولیهی کش L1 و L2 پیش از این در هستههای A73 نیز شاهد اورهال اساسی بوده است، اما آرم برای پردازش بهتر عملیات خارج از نوبت، واکش اولیه را در A75 دوباره مورد بازنگری قرار داده است.

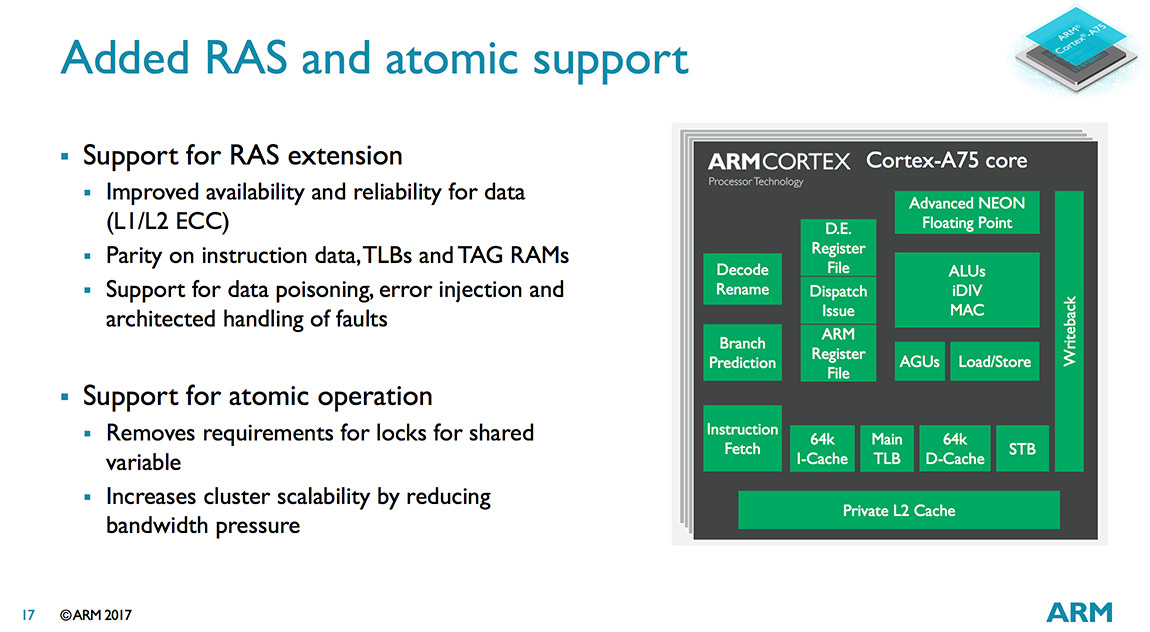

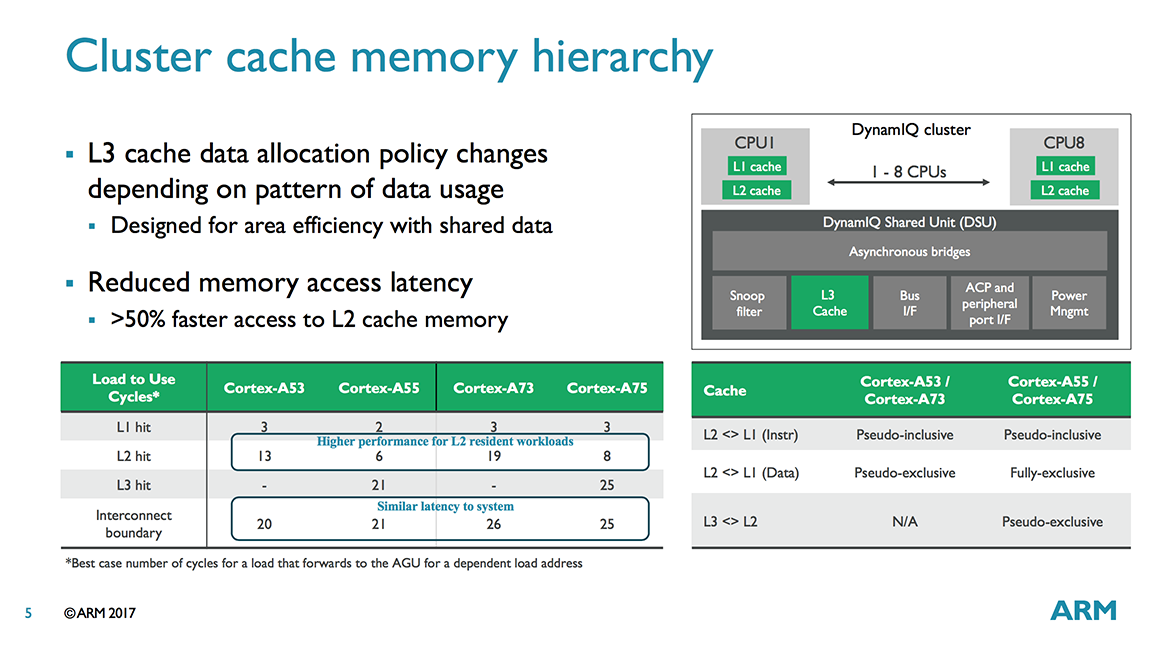

D-کش L1ا ۶۴ کیلوبایتی A73 در A75 نیز تقریبا بدون تغییر باقی مانده است؛ اما تغییر مهم در کش هستهی جدید، استفاده از کش L22 اختصاصی و ادغامشدهای است که با سرعت فرکانس خود هسته کار میکند. کش جدید در مقایسه با کش L2 اشتراکی مورد استفاده توسط هستههای A73، میزان تأخیر را تا ۵۰ درصد کاهش میدهد.

سازندههای SoC میتوانند در هستههای جدید از ۲۵۶ یا ۵۱۲ کیلوبایت کش L2 انتخابی استفاده کنند. استفاده از گزینهی ۵۱۲ کیلوبایتی عملکرد تکهستهی پردازنده را تنها ۲ درصد در مقایسه با کش ۲۵۶ کیلوبایتی افزایش میدهد؛ اما عملکرد چندهستهی پردازنده را (درصورتی که از چهار هستهی A75 و تکنولوژی DynamIQ در آن استفاده شده باشد) تا ۵ درصد افزایش میدهد. نوع بافر تیالبی اصلی در A75 نیز دستخوش تغییر شده است و بافر استور (STB) هم به ۷ اسلات ۱۲۸ بیتی افزایش پیدا کرده است.

در نهایت به پایپلاینهای اجرایی میرسیم. پایپلاینهای ALU/INT درست مانند A73 هستند؛ به این معنی که A75 همچنان نمیتواند دو عمل ضرب یا تقسیم صحیح را بهصورت موازی انجام بدهد. جالب است بدانید آرم پس از مهاجرت به دیکود سه مرحلهای، در نظر داشته است از یک پایپ ALU/INT اضافه نیز استفاده کند، اما پس از انجام آزمایش متوجه شده است میزان بهبود عملکرد ناشی از پایپ جدید، نمیتواند افزایش مصرف هسته را توجیه کند.

دو پایپ ۶۴ بیت NEON/ممیز شناور، مرحلهی Rename و فایل رجیستر ۱۲۸ بیتی اختصاصی خود را دارند که قادر به انجام ۸ عملیات ۸ بیتی صحیح، ۴ عملیات ۱۶ بیتی صحیح، ۲ عملیات ۳۲ بیتی صحیح یا ممیز شناور، یا ۱ عملیات ۶۴ بیتی ممیز شناور دو دقتی در هر سیکل است. این موضوع دست برنامهنویسان را برای در اولویت قرار دادن دقت یاعملکرد در برنامههایشان باز میگذارد.

همچنین به لطف استفاده از معماری ARMv8.2، هستههای A75 بهصورت بومی از عملیات نیم دقتی FP16 پشتیبانی میکنند. استفاده از دادههای کم دقتتر (مانند استفاده از دادههای ۱۶ بیتی در FP16 در مقایسه با دادههای ۳۲ یا ۶۴ بیتی) میزان مموری یا کش مورد نیاز برای ذخیرهی دادهها را کاهش میدهد و باعث افزایش پهنای باند میشود. این معاوضهی دقت با عملکرد، در کاربردهایی مانند یادگیری ماشینی یا پردازش تصویر میتواند بسیار مفید باشد. A73 و دیگر هستههای big نیز پیش از این میتوانستند مقادیر FP16 را از مموری دریافت کنند؛ اما قبل از پردازش مجبور بودند آنها را به FP32 تبدیل کنند که باعث کاهش عملکرد هسته میشد.

در بسیاری از الگوریتمهای شبکههای عصبی پس از اینکه فرآیند آموزش به پایان میرسد، دقت به ۸ بیت کاهش پیدا میکند. برای سرعت دادن به اجرای این نوع الگوریتمها، A75 (یا به بیان دقیقتر معماری ARMv8.2) از مجموعه دستورالعملهای جدید ضرب نقطهای INT8 استفاده میکند که باعث کاهش شدید زمان تأخیر میشود.

در پایان، مهمترین تغییرات هستهی جدید A75 نسبت به نسل قبل را میتوان اینطور خلاصه کرد:

- استفاده از معماری جدید ARMv8.2 (در مقایسه با معماری ARMv8.0 کورتکس A73)

- استفاده از تکنولوژی جدید DynamIQ بهعنوان جایگزینی برای big.LITTLE

- کش L2 اختصاصی و بهبودیافته

- استفاده از کش L3 برای اولین بار

- اضافه شدن یک مرحله و یک پایپ جدید به پایپلاین دستورالعمل

- استفاده از مجموعهی جدید دستورالعملهای NEON برای سرعت دادن به شبکههای عصبی و پردازش تصاویر

در قسمت بعدی به بررسی ریز معماری A55 خواهیم پرداخت.

ادامه دارد...

ARM بهتازگی از هستههای پردازشی Cortex-A75 ،Cortex-A55 و هستههای گرافیکی Mali-G72 برای استفاده در دستگاههای موبایل رونمایی کرده است. هستههای جدید ARM برمبنای معماری ARMv8.2-A برای استفاده در نسل جدید سیستمهای روی چیپ (SoC) طراحی شدهاند. باتوجه بهاینکه این هستهها قرار است در قلب بسیاری از پردازندههای جدید از جمله اسنپدراگون 845 کوالکام قرار بگیرند، و ازطرفی با توجه به اعلام کوالکام و مایکروسافت مبنی بر اجرای نسخهی کامل ویندوز 10 روی این پردازندهها، آشنایی با معماری هستههای ARMM بسیار مفید خواهد بود.

بههمین منظور قصد داریم طی مقالهای سه قسمتی در زومیت، به بررسی دقیق جزئیات فنی و ویژگیهای جدید معماری هستههای کورتکس ARM بپردازیم. قسمت اول این مجموعه به بررسی تکنولوژی DynamIQ (بخوانید داینامیک) اختصاص دارد.

مقدمه

ARM با توجه به نیاز شرکای سختافزاری خود و پیشرفت سریع دستگاهها در قسمتهایی مانند نمایشگر و هوش مصنوعی، مجبور است ریزمعماری پردازندههای خود را بهصورت سالانه بهروزرسانی کند. بههمین منظور، چندین تیم توسعه در نقاط مختلف دنیا بهصورت موازی و همزمان مشغول کار روی طراحیهای جدید برای ARM هستند.

سال گذشته در جریان کنفرانس سالانهی TechDay در آستین تگزاس، ARM از هستههای گرافیکی Mali-G71 با معماری جدید Bitfrost و هستههای پردازشی Cortex-A73 بهعنوان جایگزینی برای A72 رونمایی کرد. نکتهی قابل توجه درجریان رونمایی از هستههای جدید در سال گذشته، عدم معرفی هستههای LITTLE در کنار هستههای big کورتکس A73 بود. (در معماری big.LITTLE، از تعدادی هستهی قوی (big) در کنار هستههای ضعیف و کممصرف (LITTLE) استفاده میشوند.)

در جریان TechDay امسال که در کمبریج انگلستان برگزار شد، ARM از هستههای گرافیکی جدید Mali-G72، هستههای پردازشی Cortex-A75 و درنهایت بالاخره از جانشین هستههای LITTLE کورتکس A53 با نام A55 رونمایی کرد.

A53 همزمان با هستهی A57 معرفی شده بود و چندین سال است که بهصورت مستقل، یا به عنوان هستهی LITTLE در چیپهایی که از معماری big.LITTLE بهره میبرند، استفاده میشود. کورتکس A53 که ظرف مدت کمتر از ۳ سال، ۱.۷ میلیارد نسخه از آن در محصولات ساخت ۴۰ شرکت استفاده شده است، یکی از موفقترین هستههای ARM تا بهامروز بهشمار میرود؛ اما عدم معرفی هستهی LITTLE جدید طی چند سال گذشته، باعث شده است تا فاصلهی قدرت پردازشی این هسته با هستههای big بسیار زیاد شود.

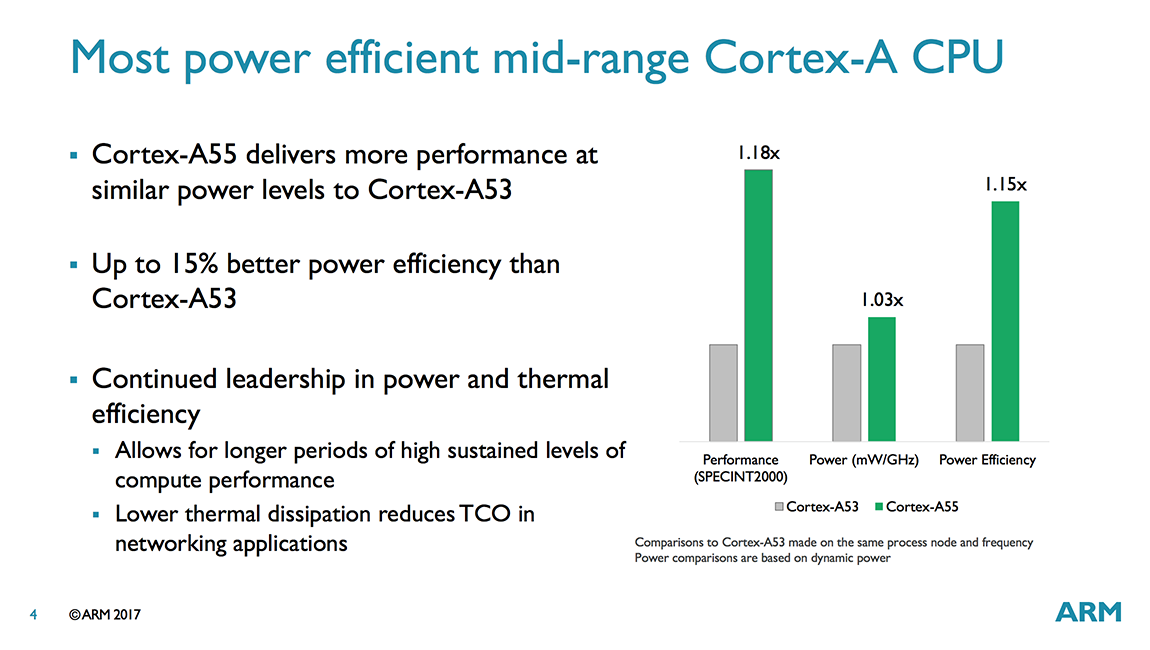

مقایسهی عملکرد A55 با A53 در فرکانس یکسان

ازآنجاییکه A53 از قبل عملکرد پردازشی نسبتا خوبی را دراختیار میگذاشت، اینبار با معرفی A55، تمرکز ARM روی بهبود سیستم مموری هستههای جدید بوده است. استفاده از کش L2 با تأخیر ۵۰ درصد کمتر نسبت به نسل قبل، بهکارگیری کش L3 برای اولین بار و دیگر بهبودهای مموری محور، باعث شده است تا عملکردهای مرتبط با مموری در A55 شاهد بهبود دو برابری در بنچمارک LMBench باشد. اعداد ارائه شده توسط ARM همچنین حاکی از بهبود ۱۸ درصدی در بنچمارک SPECint 2006 و بهبود ۳۸ درصدی در SPECfp 2006 هستند.

این مقادیر و درصدهای نشاندادهشده در نمودارها، همگی مربوط به مقایسهی A53 و A55 با فرکانس، کش L1 و L2 و کامپایکر کاملا یکسان است. ازآنجایی که سازندگان تراشه احتمالا از فرکانس بالاتر به همراه مقداری کش L3 در SoC-های مبتنی بر A55 استفاده خواهند کرد، نتایج واقعی احتمالا از اعداد و ارقام ارائه شده توسط ARM نیز بهتر خواهد بود.

مقایسهی توان، عملکرد و بهینگی مصرف انرژی هستههای A53 و A55

این افزایش عملکرد البته باعث افزایش ۳ درصدی مصرف انرژی در هستههای A55 شده است؛ اما با توجه به نتایج بنچمارک SPECint 2000، در عین حال بهینگی مصرف انرژی نیز ۱۵ درصد بهبود یافته است.

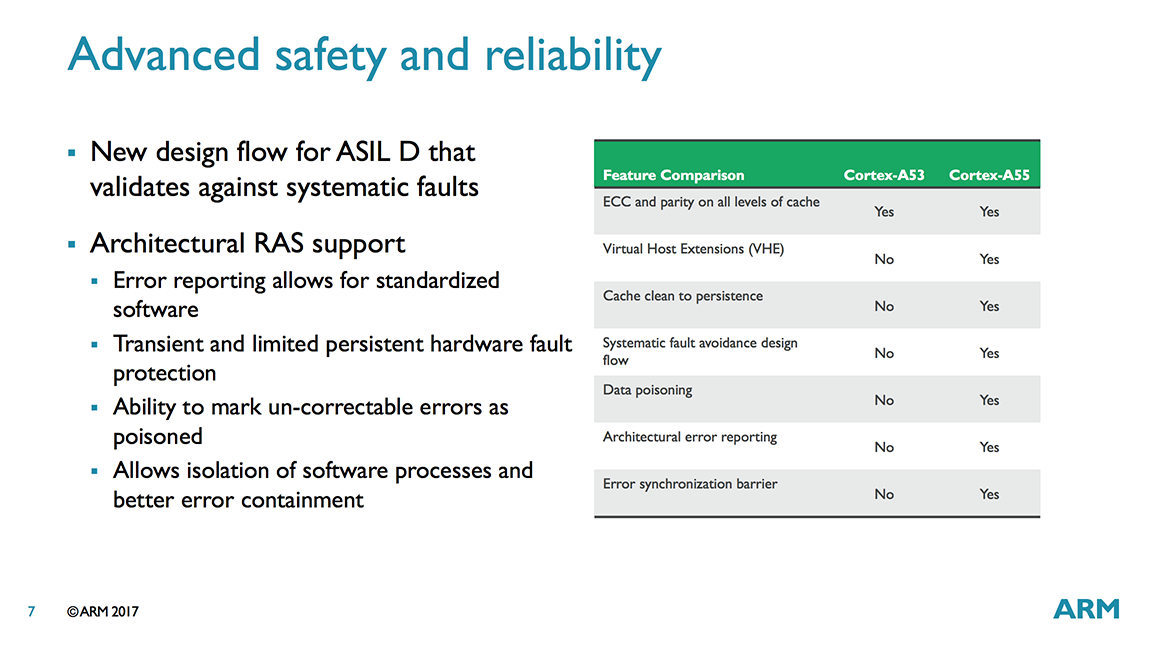

A55 همچنین به قابلیتهایی جدید برای استفاده در دستگاههایی بهغیر از تلفنهای هوشمند مجهز شده است. برای مثال Virtual Host Extensions) VHE) و پشتیبانی از سرویسهای دسترسی از راه دور (RAS)، از جمله قابلیتهای جدیدی هستند که برای خودروهای خودران بسیار مهم بهشمار میروند و اضافه شدن مجموعه دستورالعملهای ضرب نقطهای Int8 (مجموعهای از دستورالعملهای جدید برای یادگیری عمیق)، A55 را برای استفاده در شبکههای عصبیمناسب میکند. همچنین ازآنجایی که A55 با DynamIQ سازگار است، میتواند به پورتهای ۲۵۶ بیت AMBA 5 CHI نیز درسترسی داشته باشد.

مجموعهای از قابلیتهای جدید هستههای کورتکس که به «امنیت» و «پایداری» سیستم کمک میکند.

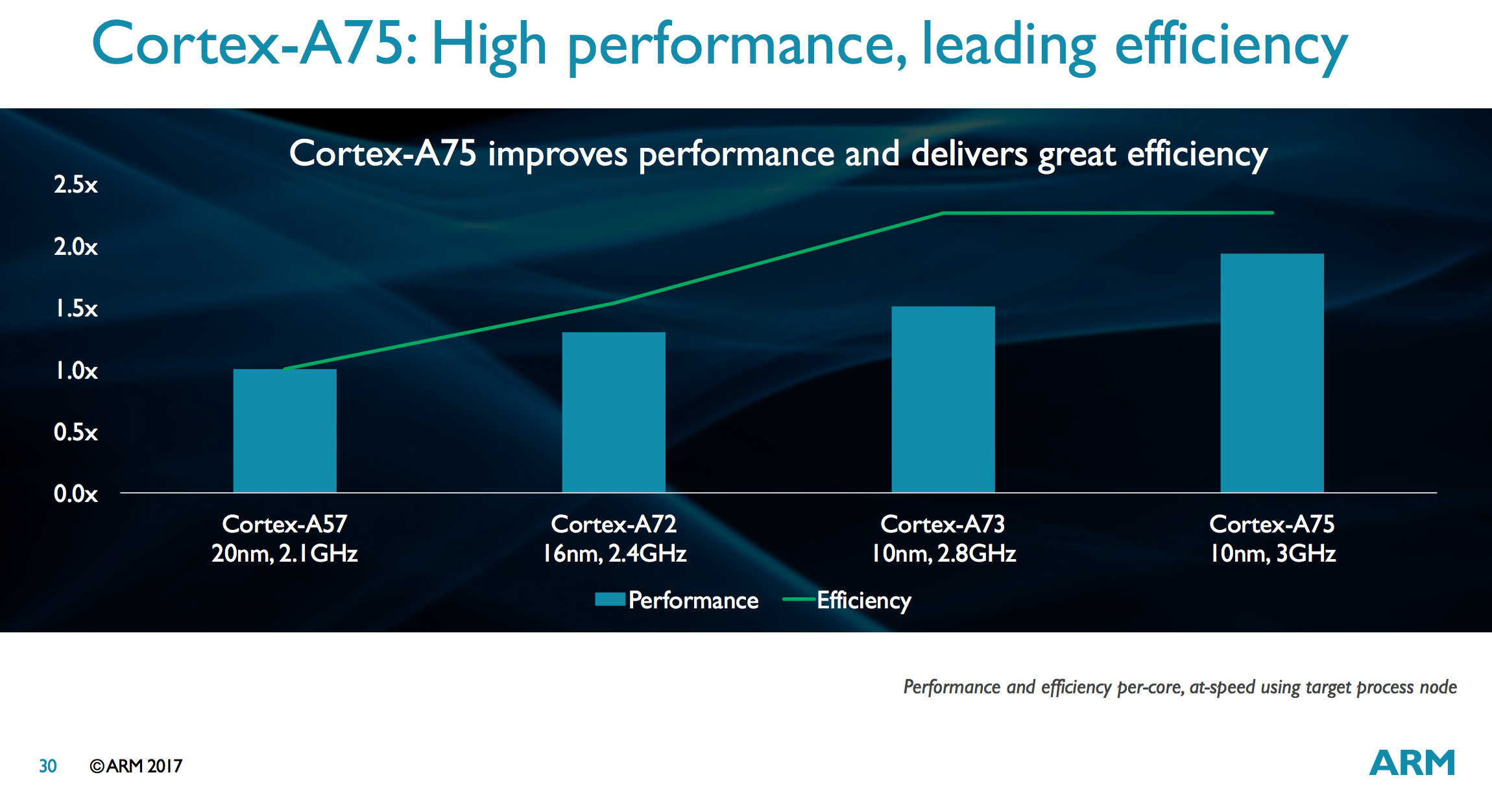

هنگامی که ARM سال گذشته هستههای A73 را معرفی کرد، روی قابلیت «عملکرد پایدار» هستههای جدید خود مانور زیادی داد. این قابلیت که در نسل جدید هستههای ARM نیز حضور دارد، باعث میشود هنگام پردازش سنگین در بازههای زمانی طولانی، عملکرد پردازنده ثابت باقی بماند و دچار افت نشود. درحالیکه ARM در طراحی A73 تمرکز اصلی خود را روی بهبود مصرف انرژی هسته قرار داده بود، در A75 با نگهداشتن بهینگی انرژی در سطحی برابر با A73، عملکرد پردازشی هسته را افزایش داده است.

عملکرد هستهی A75 در مقایسه با A73 افزایش قابل توجهی داشته است.

A73 بهدلیل بهرهگرفتن از معماری کاملا متفاوت با A72، نتایج نسبتا عجیبی در بنچمارکها از خود نشان میداد. درحالی که عملکرد محاسبات صحیح (Integer Performance) هستهی جدید نسبت به A722 بهبود پیدا کرده بود، اما درمحاسبات ممیز شناور A73 شاهد افت عملکرد نسبت به هستههای قدیمی بود. خوشبختانه ظاهرا این مشکل در A75 برطرف شده است؛ چرا که باتوجه به اعداد ارائه شده توسط ARM، هستههای A75 هم در محاسبات صحیح و هم ممیز شناور، بهبود قابل توجهی نسبت به A73 دارند.

مقایسهی عملکرد و بازده هستههای A57، A72، A73 و A75

نمودار بالا نشان میدهد که A75 در سرعت کلاک ۳ گیگاهرتز روی گرههای ۱۰ نانومتری، عملکردی بهتر از هستههای A73 در کلاک ۲.۸ گیگاهرتز روی گرههایی با همان اندازه از خود نشان میدهد، و در عینحال بازده انرژی آن نیز ثابت باقی مانده است. این به معنی افزایش مصرف انرژی هستههای جدید است. برای کنترل کردن دمای تولید شده توسط پردازنده، ARM در A72 هنگام استفاده از ۴ هسته بهصورت همزمان، عملکرد هسته را در یک بازهی ترمالِ مشخص محدود کرده بود. ARM در A75 نیز برای دستیابی به عملکرد پایدار، از تکنیک «بازهی ترمال تعریف شده» استفاده کرده است. البته استفاده از هر ۴۴ هسته بهصورت همزمان سناریوی متداولی در تلفنهای هوشمند نیست، چراکه اکثر برنامههای موبایل نهایتا از یک تا دو هسته بهصورت همزمان، آنهم در بازههای کوتاه زمانی استفاده میکنند.

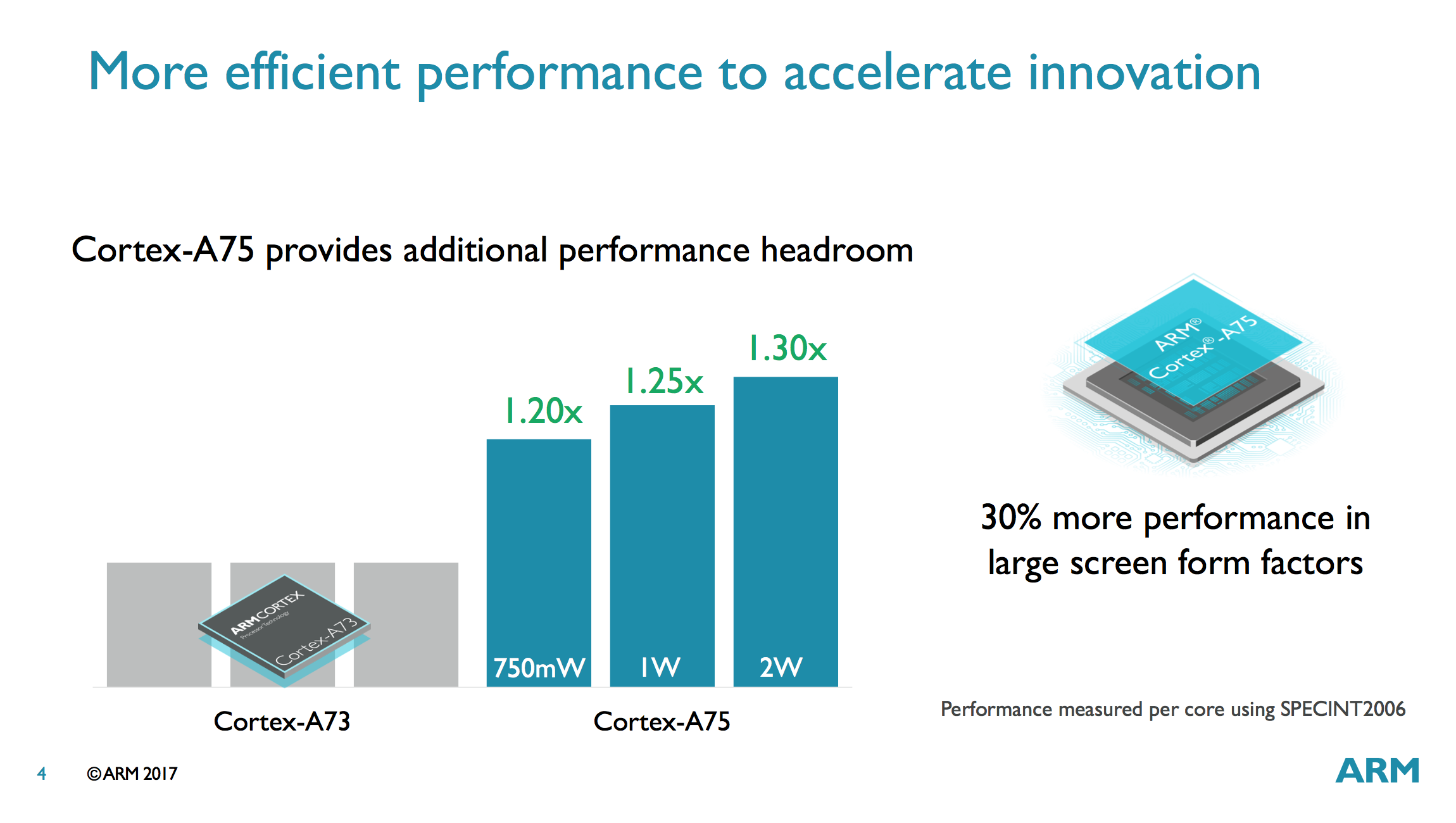

ARM در A75 محدودیت مصرف ۷۵۰ میلیواتی هسته را برداشته است؛ اما با افزایش توان هسته از ۱ به ۲ وات،

تنها شاهد افزایش ۵ درصدی عملکرد آن هستیم.

ARM همچنین با افزایش فرکانس و عبور از سد محدودیت توان مصرفی ۷۵۰ میلیوات در هر هسته، قصد دارد A75 را به گزینهای برای استفاده در دستگاههایی با فرمفاکتور بزرگتر تبدیل کند. با این کار، استفاده از هستههای A75 درکرومبوکها و لپتاپهای ویندوزی (در صورت ارائهی ویندوز 10 سازگار با ARMM توسط مایکروسافت) ممکن میشود.

افزایش توان مصرفی به ۱ وات بر هسته، باعث میشود عملکرد A75 تا ۲۵ درصد نسبت به A73 بهبود پیدا کند؛ اما با افزایش توان به ۲ وات بر هسته، تنها شاهد افزایش ۳۰ درصدی عملکرد هستههای جدید خواهیم بود. این اعداد و ارقام یکی از بهترین مثالها برای نشان دادن این اصل مهم هستند که «افزایش صرف فرکانس هسته به معنی بهبود عملکرد پردازشی CPU نیست»؛ چرا که با بالارفتن سرعت کلاک، مصرف انرژی بهصورت لگاریتمی بالا میرود.

ARM با تمرکز بر بهینگی مصرف انرژی، ویژگیهایی مانند استفاده از ECC در کش L1 و دسترسی به پورت ۲۵۶ بیتی AMBA 5 CHI را بهمنظور کاهش پیچیدگی طراحی هسته از A73 حذف کرده بود؛ چرا که قصد داشت پردازندهای کممصرف و ساده دراختیار تولیدکنندگان دستگاههای موبایل قرار بدهد. با معرفی هستههای جدید اما ARM با گنجاندن ویژگیهای متعدد در A75، آن را برای استفاده در سرورها، خودروهای خودران و دیگر مصارف آماده کرده است.

DynamIQ

تکنولوژی big.LITTLE آرم که ۵ سال پیش معرفی شد، اجازه میداد تا چندین کلاستر (تا ۴ CPUU) بهصورت زنجیرهای با هم ترکیب شوند. با استفاده از big.LITTLE این امکان بهوجود میآمد تا ترکیبهای مختلفی از هستههای خانوادهی Cortex-A درکنار یکدیگر بهکار گرفته شوند و درنتیجه ساخت طیف وسیعی از پردازندهها (از پردازندهی تلفنهای پایینرده و مقرونبهصرفه گرفته تا دستگاههای پرچمدار گرانقیمت) میسر میشد.استفاده از تکنولوژی big.LITTLE برای ترکیب هستههای کورتکس تنها به تلفنهای هوشمند و تبلتها محدود نمیشد؛ بلکه طی این سالها شاهد استفاده از پردازندههای مبتنی بر این تکنولوژی در سرورها و خودروهای خودران نیز بودهایم.

با تغییر ساختار و کارایی دستگاههای مبتنی بر ARM طی سالهای اخیر، نیاز به تکامل تکنولوژی big.LITTLE بهشدت احساس میشد. ARM نیز که بهتر از همه به این موضوع واقف بود، همزمان با رونمایی از جدیدترین هستههای خود، نسخهی جدید big.LITTLE را با نام DynamIQ معرفی کرد. بهگفتهی ARM، توسعهی DynamIQ از سال ۲۰۱۳ شروع شده و از آن زمان تاکنون، تغییرات زیادی بهخود دیده است. باتوجه به زمان نسبتا طولانی توسعهی DynamIQ، انتظار میرود تا چندین سال شاهد استفادهی بدون تغییر از آن در پردازندههای ARM باشیم.

با استفاده از DynamIQ میتوان هستههای big و LITTLE را با کش اختصاصی در یک کلاکستر استفاده کرد

درست مانند big.LITTLE، تکنولوژی DynamIQ نیز امکان گروهبندی CPU در کلاستر و متصل کردن آن به دیگر پردازندهها (برای مثال پردازندهی گرافیکی) و دیگر سختافزارهای سیستم را فراهم میکند؛ اما تفاوتهای بزرگی در نحوهی انجام این کار بین دو تکنولوژی مذکور وجود دارد. برای شروع، بزرگترین تغییر ایجاد شده در DynamIQ، امکان استفادهی همزمان از هستههای big و LITTLE در یک کلاستر است. (تا پیش از این هستههای کورتکس متفاوت باید در کلاسکرهای جدا از هم استفاده میشدند.) همین تغییر بهظاهر ساده، علاوه بر بالابردن عملکرد پردازنده، دست سازندگان SoC را برای بهکارگیری ترکیبهای بسیار متنوعتر از هستهها باز خواهد گذاشت.

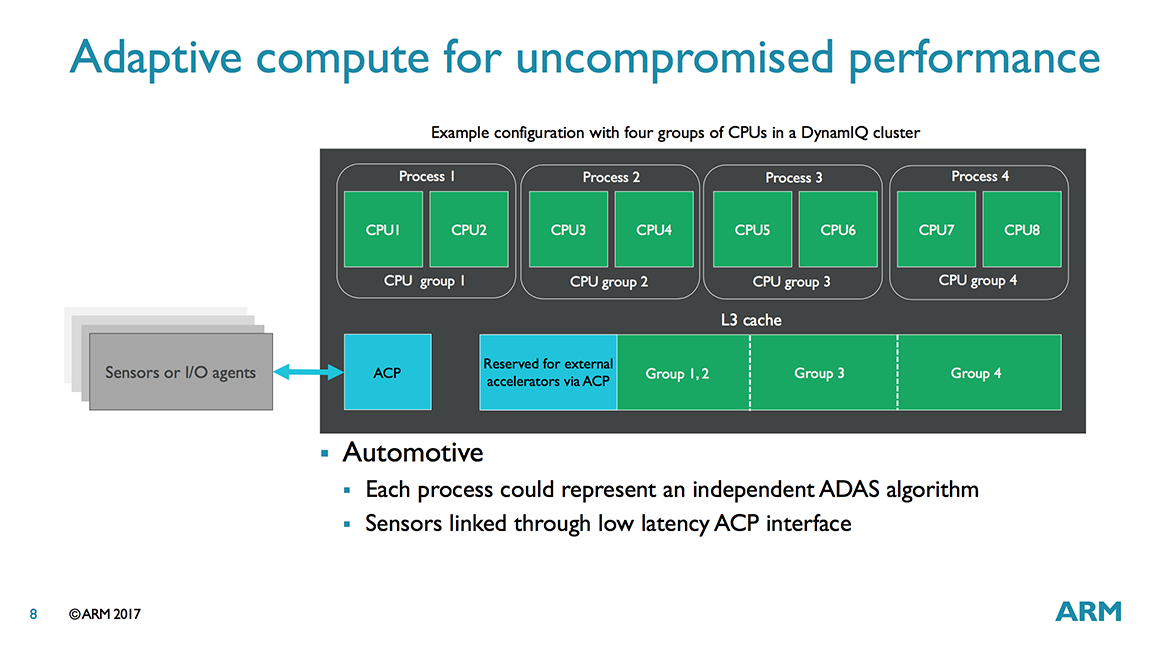

تغییر بزرگ بعدی، امکان گنجاندن تا ۸ CPU در یک کلاستر، و افزایش ماکزیمم تعداد کلاسترها به ۳۲ عدد است. درنتیجه با استفاده از تکنولوژی DynamIQ میتوان تا ۲۵۶ CPU را در یک چیپ جای داد.

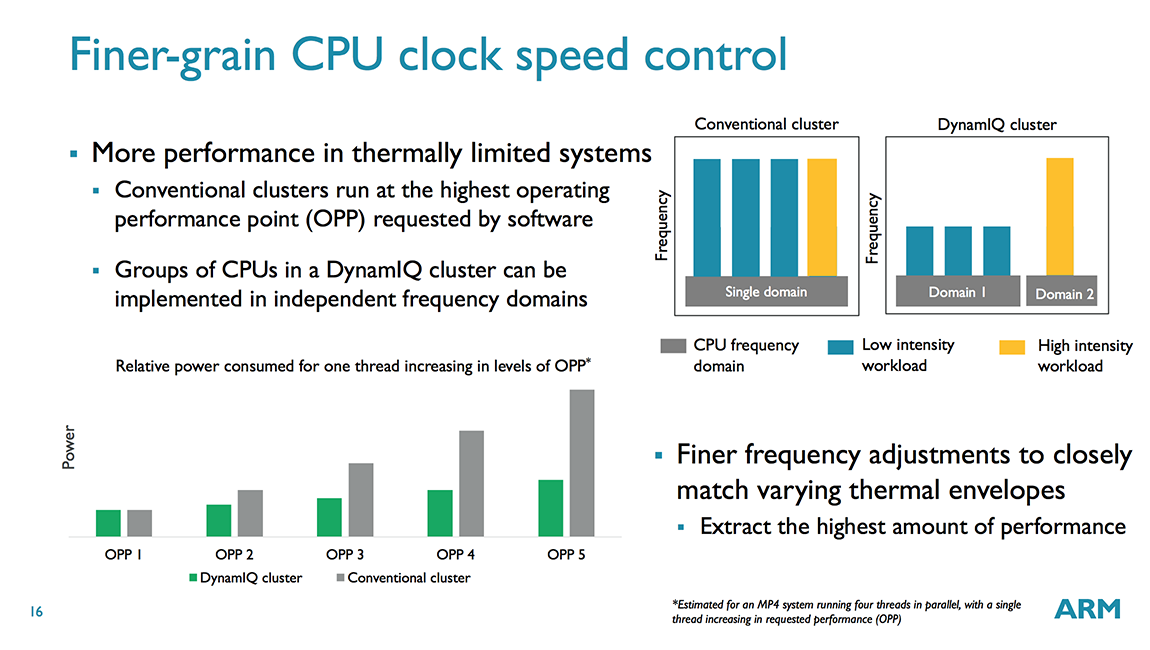

درون هر کلاستر، CPU بر اساس ولتاژ یا فرکانس در دامنههای متفاوت تقسیمبندی میشوند و درون هر دامنه، هستهها با توجه به توان مصرفی درون زیردامنههای خود قرار میگیرند. این کار باعث میشود بتوان مصرف هر CPU را جدا از CPU-های دیگر، بهصورت مجزا کاهش یا افزایش داد. با استفاده از DynamIQ هر کلاستر میتواند تا ۸ ولتاژ یا فرکانس متفاوت را پشتیبانی کند.

آنچه در بالا گفته شد به بیان ساده یعنی در حالت تئوری، سازندگان SoC قادر خواهند بود تا CPU-هایی با ولتاژ و فرکانس متفاوت و مستقل از یکدیگر را درون یک کلاستر قرار بدهند. این موضوع باعث میشود یک هستهی پرمصرف، ولتاژ و فرکانس بالای خود را به هستههای کممصرف تحمیل نکند و درنتیجه بهینگی مصرف انرژی دستگاه تا حد زیادی بهبود پیدا کند. البته هر دامنهی فرکانسی به رگولاتور ولتاژ مخصوص به خود نیاز دارد که موجب افزایش هزینه و پیچیدگی طراحی SoC خواهد شد. برای همین، احتمالا مانند سابق شاهد استفاده از حداکثر ۲ تا ۴ CPU در هر کلاستر خواهیم بود.

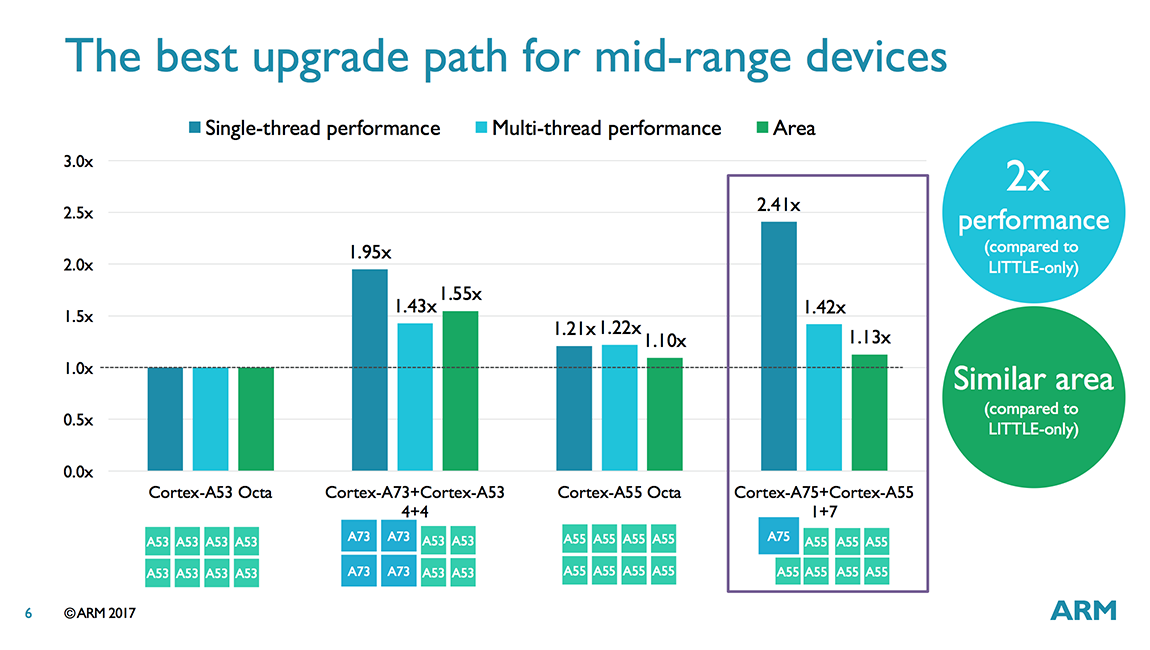

مقایسهی عملکرد ترکیبهای مختلف هستههای کورتکس در یک پردازندهی ۸ هستهای

ARM عقیده دارد طی سالهای آینده، صنعت موبایل همچنان شاهد استفاده از پردازندههای ۸ هستهای در دستگاههای موبایل خواهد بود. تاکنون با استفاده از تکنولوژی big.LITTLE، ترکیب ۸ هسته یا بهصورت ۴+۴ (که در آن از ۴ هستهی big در کنار ۴ هستهی LITTLE در دو کلاستر استفاده میشد) در دستگاههای بالارده، یا بهصورت استفاده از ۸ هستهی LITTLE در دستگاههای پایینرده بوده است. با تکنولوژی DynamIQ اما هستههای A75 یا A55 میتوانند با هر ترکیب دلخواهی (برای مثال ۱+۷، ۲+۶، ۳+۵ و ۴+۴) درون یک کلاستر در کنار یکدیگر قرار بگیرند.

ARM عقیده دارد از میان ترکیبهای ممکن، ترکیب ۷ هستهی کممصرف A55 با یک هستهی big از نوع A75 برای دستگاههای میانرده بسیار مناسب خواهد بود؛ چرا که تنها با افزایش ۱.۱۳ برابری مساحت تراشه، عملکرد تکهستهی آن ۲.۴۱ برابر و عملکرد چند هستهای آن ۱.۴۲ برابر نسبت به پردازندههایی که هر ۸ هستهی آنها A53 (با کلاک برابر) است، افزایش خواهد یافت.

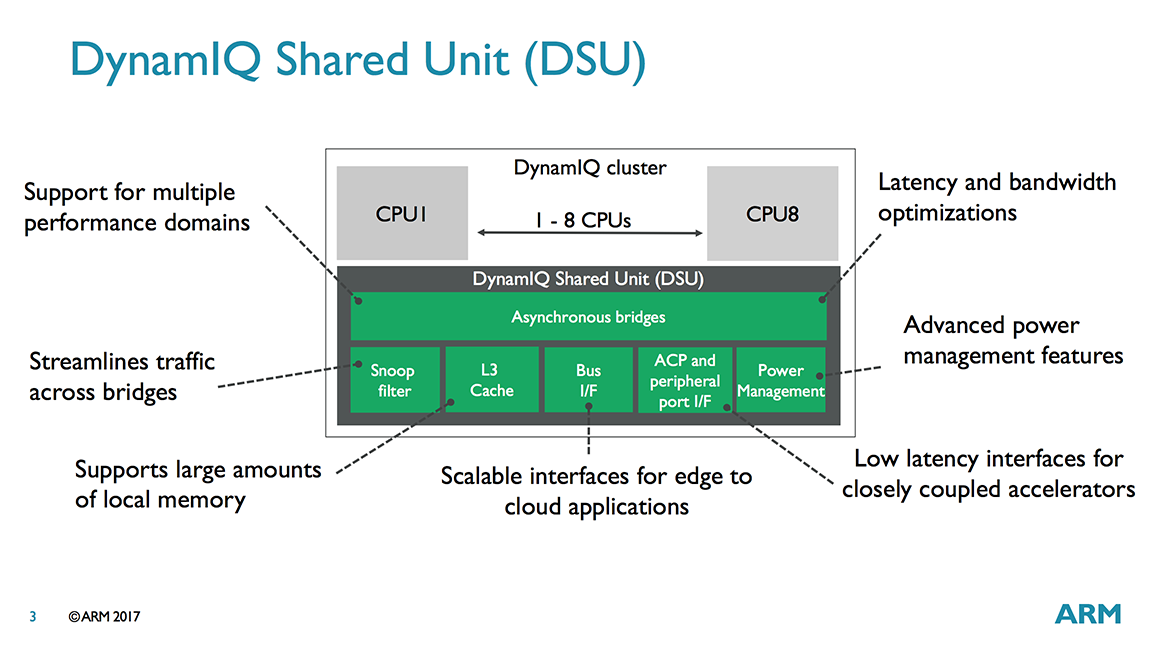

DSU نام بلوک جدیدی در معماری ARM است که حافظهی کش L3 درون آن قرار دارد

مهمترین قطعهی پازل DynamIQ، که باعث میشود هستههای پردازشی درون یک کلاستر بتوانند در فرکانسهای متفاوت و مستقل از یکدیگر کار کنند، بلوک جدیدی با نام DynamIQ Shared Unit) DSU) است. بلوک DSU درواقع نقش یک هاب مرکزی را در هر کلاستر بازی میکند که هستهها با ولتاژهای مختلف، از طریق آن با بقیهی سیستم ارتباط برقرار میکنند.

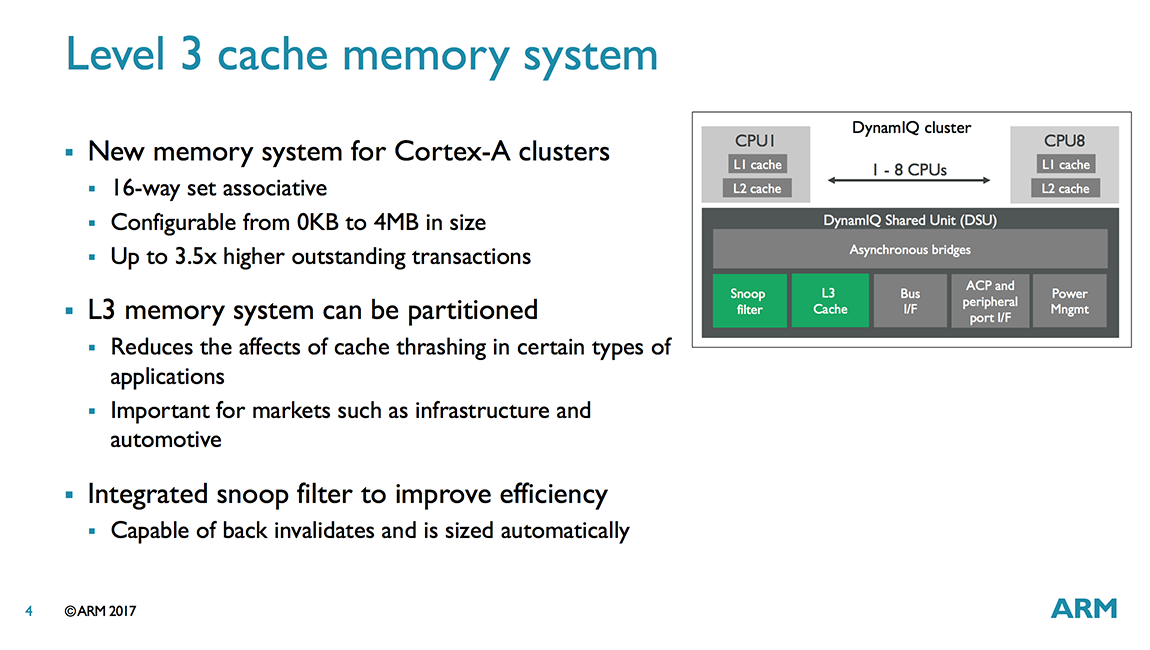

کش L3 بهکار رفته در DSU از نوع شبهاختصاصی است

تا بهحال هرچه از DynamIQ گفتیم مربوط به توانایی آن در بهکارگیری هستههای مختلف درکنار یکدیگر بوده است. اما این تکنولوژی علاوه بر ایجاد انعطاف در ترکیب هستههای درون یک کلاستر، بهبود عملکرد CPU را نیز با خود به ارمغان میآورد. با استفاده از تکنولوژی big.LITTLE،اCPU-های درون یک کلاستر میتوانستند بهصورت اشتراکی از یک کش L2 استفاده کنند؛ اما با آمدن DynamIQ،اCPU-های سازگار با این تکنولوژی (درحال حاضر تنها A75 و A55) امکان دسترسی به کش L2 اختصاصی، با فرکانس برابر با هستهی خود را دارند. انتقال کش L2 به نزدیکی هسته، میزان تأخیر آن را تا ۵۰ درصد کاهش میدهد. DynamIQ همچنین سطح جدیدی از کش را به تراشه اضافه میکند. کش L3 اضافه شده که استفاده از آن توسط سازندگان SoC اختیاری خواهد بود، درون DSU قرار میگیرد. مقادیر کش L3 در معماری جدید ARM میتواند ۱، ۲ یا ۴ مگابایت باشد و بهصورت اشتراکی از آن استفاده خواهد شد.

کش L3 بهصورت کلی میتواند «فراگیر» یا «اختصاصی» باشد. کش L3 فراگیر یک کپی کامل از کش L2 پردازنده را نیز درخود جای میدهد که باعث کاهش شدید عملکرد و هدر رفتن فضا و توان مصرفی آن میشود. گرچه حافظهی کش L3 بهکار رفته در DSU-های ARM از نوع «شبه اختصاصی» است، اما ARM ادعا میکند این حافظه به کشهای L3 اختصاصی بسیار نزدیکتر است تا فراگیر.

آوردن کش L2 به درون کلاستر و قرار دادن آن در نزدیکی هسته، میزان تأخیر آن را تا ۵۰ درصد کاهش میدهد

کش L3 درون DSU میتواند پارتیشنبندی شود که برای استفاده در سامانههای نهفته (امبدد) که بار کاری ثابتی دارند، بسیار مفید خواهد بود. این حافظه میتواند به ۴ پارتیشن با سایزهای متفاوت تقسیم شود، درنتیجه یک CPUU میتواند مثلا از ۳ مگابایت، و هفت CPU دیگر در مجموع از ۱ مگابایت کش L3 بهصورت اشتراکی استفاده کنند.این پارتیشنها از نوع دینامیک خواهند بود و میتوان حین اجرای برنامهها توسط سیستم عامل آنها را تولید یا تغییر اندازه داد.

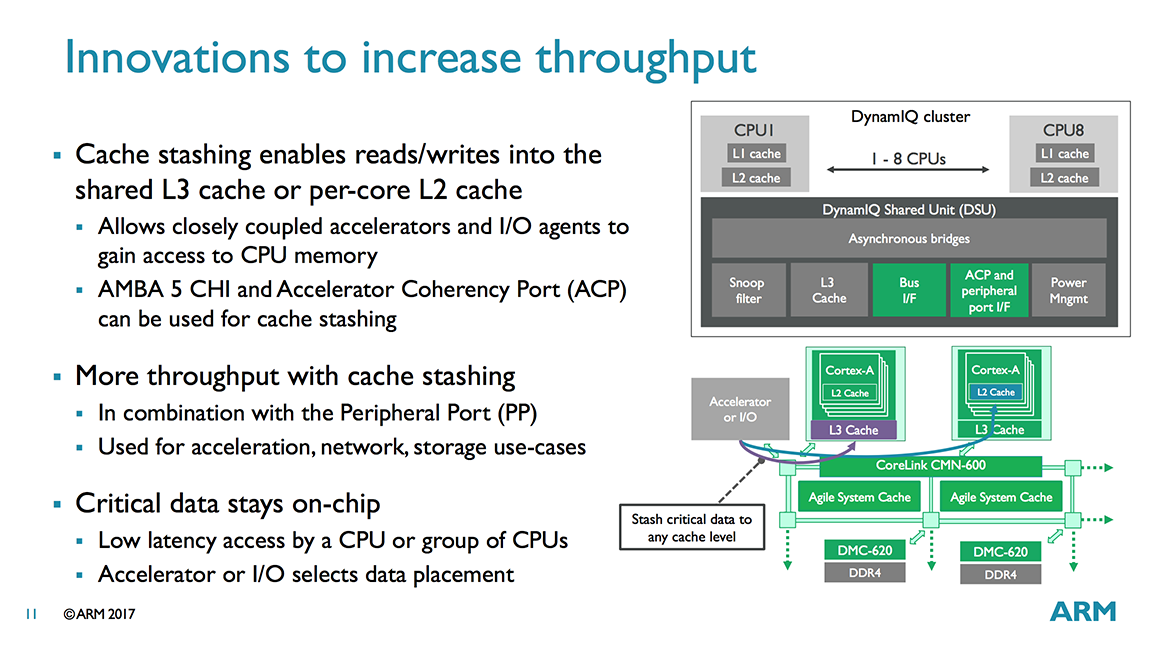

از دیگر ویژگیهای DynamIQ میتوان به قابلیت «ذخیره روی کش» (cache stashing) اشاره کرد که به GPU یا دیگر شتابدهندههای سختافزاری و ایجینتهای I/O اجازه میدهد تا از طریق رابط ACP یا پورت AMBA 5 CHII بهصورت مستقیم اطلاعات را روی کش L2 و L33 بنویسند یا از روی آن بخوانند. به عنوان مثال میتوان به عملکردهای مرتبط با شبکه اشاره کرد که در آنها با استفاده از مجموعه پروتکلهای TCP/IP،پَکِتهای شبکه پردازش میشوند. در این حالت موتور شتابدهنده بهجای نوشتن دادهها روی رم سیستم (یا هر مکانیزم کش دیگر) و سپس منتقل کردن آن به CPU برای پردازش، میتواند با استفاده از قابلیت ذخیره روی کش، دادهها را بهصورت مستقیم روی کش L2 پردازنده بنویسد. با این کار عملکرد طیف وسیعی از برنامهها افزایش، و مصرف انرژی کاهش پیدا میکند.

با استفاده از قابلیت ذخیره روی کش (cache stashing)، سختافزارهای خارج از کلاستر نیز میتوانند به کش L2 و L3 دسترسی داشته باشند.

برای استفاده از قابلیت ذخیره روی کش، درایورهای نرمافزاریِ کرنل باید از پردازنده و توپولوژی کش آگاه باشند؛ درنتیجه برای فراهم کردن امکان دسترسی سختافزارهای خارج از کلاستر به کش L2 اشتراکی، نیاز به اضافه کردن کدهای اختصاصی جدید به درایورهای نرمافزاری وجود دارد. ازآنجاییکه بسیاری از دستگاههای مصرفی مانند تلفنهای هوشمند همواره با مشکل «محدودیت زمانی» برای عرضه به بازار روبهرو هستند، شاید بسیاری از تولیدکنندگان زحمت اضافه کردن کد برای استفاده از این قابلیت را بهخود ندهند و درنتیجه موج اول دستگاههای مجهز به هستههای جدید ARM از این قابلیت جدید و کاربردی محروم باشند.

یکی از ویژگیهای بلوک DSU، مدیریت سختافزاری توان مصرفی پردازنده است

علاوه بر اشتراک منابع با سختافزارهای خارج از کلاستر، DynamIQ اشتراک داده بین CPU-های درون یک کلاستر را نیز راحتتر کرده است. همین موضوع مهمترین دلیلی بود که ARM را بر آن داشت تا CPU-های big و LITTLE را این بار درون یک کلاستر در کنار هم قرار دهد. انتقال اطلاعات کش درون یک کلاستر بسیار سریعتر از انتقال آن بین دو یا چند کلاستر است و علاوه بر آن زمان تأخیر کش نیز بسیار کاهش پیدا میکند.

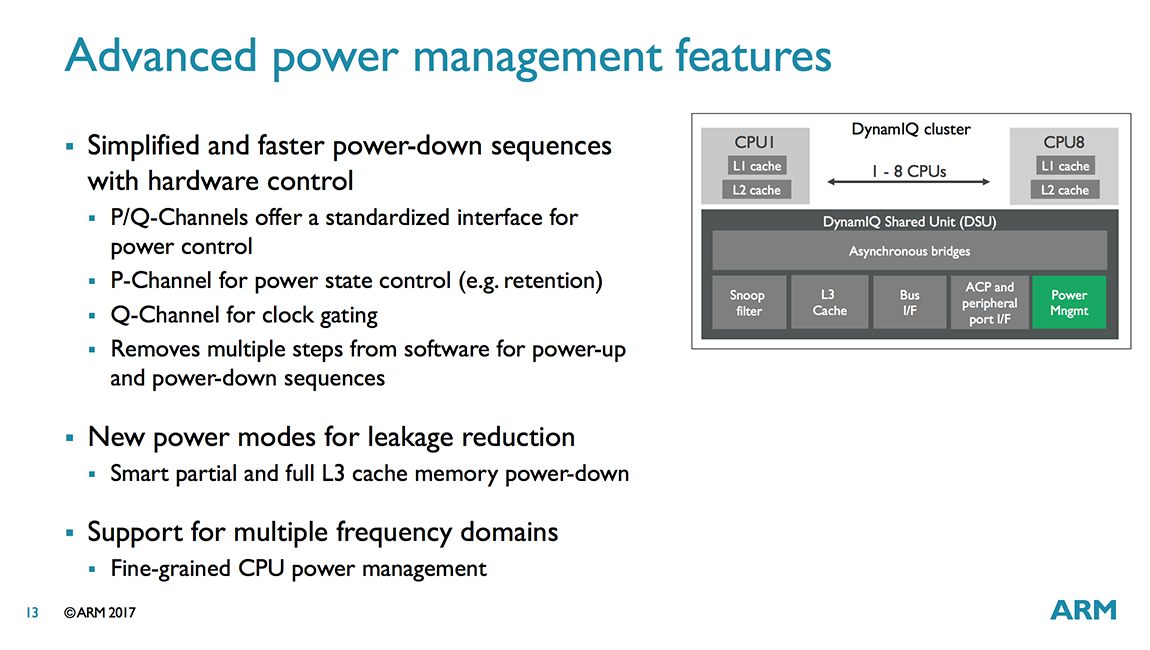

DynamIQ همچنین دارای مجموعهای از ویژگیهای پیشرفته برای مدیریت مصرف انرژی پردازنده است. برای مثال، مدیریت کش در معماری جدید توسط DSU و بهصورت سختافزاری انجام میشود. برخلاف مدیریت نرمافزاری، هنگام تغییر دادن وضعیت توان CPU توسط DSU و بهصورت سختافزاری، احتیاج به طی مراحل اضافه از بین میرود و درنتیجه میتوان قدت هستههای CPU را بسیار سریعتر از پیش افزایش یا کاهش داد.

ازآنجایی که بهکاربردن تکنولوژی جدید در پردازندهها نیازمند صرف زمان و هزینه است، شاید برخی تولیدکنندگان SoC ترجیح بدهند همچنان از تکنولوژی big.LITTLE در سیستمهای روی چیپ خود استفاده کنند. اما ازآنجایی که استفاده از تکنولوژی جدید با نامی پرطمطراق میتواند از لحاظ بازاریابی محصول به نفع تولید کننده تمام شود (مخصوصا در تلفنهای هوشمند پرچمدار)، احتمالا در آیندهای نزدیک شاهد بهکارگیری این تکنولوژی در پردازندهی دستگاههای بالارده خواهیم بود. انتظار میرود اولین SoC-های مجهز به تکنولوژی DynamIQ در اواخر سال ۲۰۱۷ یا اوایل ۲۰۱۸ به بازار عرضه شوند.

در قسمت بعدی با ریزمعماری هستههای Cortex-A75 بیشتر آشنا خواهیم شد.

خودروهای خودران بدون شک آیندهی صنعت حمل و نقل را تشکیل میدهند. بزرگترین خودروسازهای جهان در کنار تعدادی از شرکتهای مطرح فناوری اعم از گوگل و اپل، سرمایهگذاری زیادی برای توسعهی فناوری خودران کردهاند تا هرچه زودتر این تکنولوژی را پیادهسازی کنند. در حال حاضر خودروهای تسلا با تجهیز به سیستم خودران سطح ۲، هوشمندترین وسایل نقلیهی موجود در بازار هستند. این در حالی است که تعداد زیادی از خودروسازان اعم از مرسدس بنز، بیامو و نیسان از عرضهی خودروهای تمام خودران در سال ۲۰۲۰ خبر دادهاند.

خودروسازی داخلی برای جلوگیری از افزایش فاصلهی خود با علم روز دنیای خودروسازی، باید سرمایهگذاری گستردهای در علوم نوین این صنعت انجام دهد. در همین حال متخصصان شرکت دانشبنیان صنعت و فناوری هوشمند خلیج فارس (PGITIC) مستقر در پارک علم و فناوری استان هرمزگان بعد از سه سال تحقیق و تست در قالب چهار گروه الکترونیک، کنترل، مکانیک و نرمافزار، موفق به طراحی و ساخت اولین سیستم هوشمند کنترل خودرو بدون راننده در ایران شدند.

پروژهی توسعهی فناوری خودران شرکت صنعت و فناوری هوشمند خلیج فارس در سال ۲۰۱۰ و با انجام فاز تحقیق و توسعه کلید خورده است. عملیات توسعهی این پروژه در سال ۲۰۱۲ رسما آغاز شده و طراحی و پیادهسازی آن در سال ۲۰۱۴ انجام شده است. در نهایت فاز اول این پروژه در سال ۲۰۱۶ بهرهبرداری شد و طی سال جاری نیز بهطور رسمی رونمایی خواهد شد.

دکتر علی فتی رئیس پارک علم و فناوری هرمزگان گفت:

این سیستم قابلیت نصب روی تمام خودروها با گیربکس اتوماتیک را دارا است. این سیستم بعد از نصب روی خودرو توانست اولین تست خود را به طول ۲۵ کیلومتر در مسیر تعیینشده بدون خطا و دخالت انسان با موفقیت به پایان برساند.

این سیستم بعد از انجام تمام آزمایشهای ایمنی در نیمه دوم سال جاری با حضور مسئولان رونمایی خواهد شد.

علیرضا شیخ جعفری مدیرعامل شرکت صنعت و فناوری هوشمند خلیج فارس در خصوص سیستم خودران توسعهی یافتهی این شرکت گفت:

با استفاده از این سیستم، خودرو میتواند بهصورت خودکار در مسیرهای شهری و بینشهری تردد کند. این سیستم از طریق سه دوربین نصبشده روی خودرو، سیستم ناوبری جهانی (GPS)، سنسورهای اولتراسونیک، اسکنر لیزری و سامانههای هوشمند میتواند ضمن تشخیص مسیر جاده و خیابان، موانع و تابلوهای راهنمایی و رانندگی، در مسیر تعیینشده با دقت و امنیت بالا تردد کند.

از دیگر ویژگیهای این سیستم هوشمند، پیادهسازی الگوریتمهای بسیار سریع و دقیق پردازش تصویر با قابلیت تشخیص انسان، خودرو، موانع، خطوط جاده و خیابان، تابلوهای راهنمایی و رانندگی در مسیر حرکت خودرو است. کنترل مرکزی این سیستم قابلیت کنترل فرمان با دقت ۰.۰۱ درجه و کنترل پدال گاز و ترمز بهصورت همزمان و با سرعت عکسالعمل ۰٫۰۰۱ ثانیه را دارا است.

مدیرعامل شرکت صنعت و فناوری هوشمند خلیج فارس در رابطه با دیگر امکانات این خودرو افزود:

این سیستم دارای دسترسی مستقیم به اینترنت برای بررسی مسیر و شرایط جاده و آب و هوا بهصورت خودکار است. همچنین این سیستم وضعیت آب و هوا را بهصورت خودکار از طریق اینترنت بررسی میکند و ضمن گزارش وضعیت آب و هوا در مسیر حرکت وجود تجهیزات ایمنی مناسب مانند زنجیره چرخ (مثلا برای آب و هوای برفی) را مورد بررسی قرار داده و آن را به شما گزارش میدهد.

در سیستم خودران طراحیشده همچنین تدابیر لازم جهت اتصال خودروها اندیشیده شده است تا با ایجاد شبکهی گستردهای از خودروهای خودران، اطلاعات لازم اعم از وضعیت ترافیکی بین خودروها منتقل شود. مدیرعامل شرکت صنعت و فناوری هوشمند خلیج فارس تصریح کرد این سیستم قابلیت شناسایی راننده از طریق پردازش تصویر را دارا است که باعث بالا رفتن امنیت میشود و سرقت ماشین را غیر ممکن میکند.

در ادامه شما را به تماشای ویدیوی منتشرشده از نحوهی عملکرد سیستم خودران طراحی شده در ایران دعوت میکنیم.

هنگامی که صحبت در مورد وسایل نقلیهی خودران به میان میآید، اکثر کاربران به خودرو، تاکسی، اتوبوس، قطار، تراموا و ... فکر میکنند. اما هواپیماها از مدتها قبل و به لطف سیستم اتوپایلوت امکان هدایت خودکار را در اختیار خلبانان قرار دادهاند و به همین دلیل منطقی است که چنین سیستمی در کشتیها نیز به کار گرفته شود.

شرکتهای حمل و نقل ژاپنی قصد دارند با همکاری کمپانیهای کشتیسازی، تکنولوژی مورد نیاز برای ناوبری خودکار کشتیهای باری را توسعه دهند. هدف از ساخت این فناوری این است که کشتیهای باری بتوانند بهصورت خودکار یا با تعداد کمی خدمه، مسیر خود را در دریا و اقیانوس پیدا کنند. بر طبق برنامهریزی صورت گرفته توسط ژاپنیها، این تکنولوژی تا سال ۲۰۲۵ در کشتیهای باری مورد استفاده قرار گرفت. فناوری مسیریابی خودکار در کشتی باعث خواهد شد سریعترین و امنترین مسیر برای رسیدن به مقصد انتخاب شود و در عین حال مصرف سوخت نیز در بهینهترین حالت ممکن باشد. در نتیجهی استفاده از فناوری مورد بحث، هزینههای حمل و نقل دریایی کاهش چشمگیری خواهند داشت و حاشیهی سود شرکتهای باربری دریایی بیشتر خواهد شد.

تکنولوژی مورد بحث علاوه بر یافتن بهینهترین مسیرها، میتواند به پیشبینی مواردی از جمله اختلال در عملکرد دستگاهها که احتمال وقوع آنها در دریا وجود دارد نیز کمک کند و در نتیجه خسارات احتمالی کاهش خواهند یافت. شرکتهای ژاپنی قصد دارند ۲۵۰ عدد کشتی باری با این تکنولوژی تولید کنند و هزینههای مورد نیاز برای انجام این کار بین کمپانیهای حمل و نقل و شرکتهای کشتیسازی تقسیم میشود. باید اشاره کنیم که برای توسعه و ساخت کشتیهای باری با سیستم ناوبری خودکار، هزینهای چند صد میلیون دلاری نیاز است.

البته ژاپن اولین کشوری نیست که به دنبال ساخت کشتیهایی با سیستم ناوبری خودکار است. شرکت معروف رولز رویس در سال ۲۰۱۶ برنامههای مشابهی برای ساخت کشتیهای باری بدون سرنشین مطرح کرد که امکان کنترل از راه دور آنها نیز وجود دارد. بنا به اعلام رولز رویس، ساخت کشتیهای بیسرنشین این کمپانی تا سال ۲۰۲۰ انجام خواهد شد.

نظر شما در این زمینه چیست؟ آیا ساخت کشتیهای خودران میتواند در صنعت حمل و نقل دریایی تغییرات چشمگیری ایجاد کند؟

.: Weblog Themes By Pichak :.